1.ping 命令PING (Packet Internet Groper),因特网包探索器,用于测试网络连接量的程序 。Ping是工作在 TCP/IP网络体系结构中应用层的一个服务命令, 主要是向特定的目的主机发送 ICMP(Internet Control Message Protocol 因特网报文控制协议)Echo 请求报文,测试目的站是否可达及了解其有关状态 。简单的说,ping 就是一个测试程序,如果 ping 运行正确,大体上就可以排除网络访问层、网卡、Modem 的输入输出线路、电缆和路由

关键字:

网络 计算机 主机 IP 网卡

IT之家 8 月 1 日消息,龙芯中科今日上午宣布,近日,基于龙架构的新一代四核处理器龙芯 3A6000 流片成功,代表了我国自主桌面 CPU 设计领域的最新里程碑成果。根据中国电子技术标准化研究院赛西实验室测试结果,龙芯 3A6000 四核处理器在 2.5GHz 运行频率下,SPEC CPU 2006 base 单线程定 / 浮点分值分别达到 43.1/54.6 分,SPEC CPU 2006 base 多线程定 / 浮点分值分别达到 155/140 分,双 DDR4-3200 内存通道 St

关键字:

龙芯中科 CPU

IT之家 8 月 1 日消息,消息源 Bionic_Squash 近日分享了英特尔尚未公布的 Lunar Lake 核显规格,预估将会在 Arrow Lake 之后发布。消息称英特尔 Lunar Lake iGPU 将基于 Battlemage 'Xe2' 架构,最高可以实现 64 EU,明显低于 Meteor Lake 的 128 EU。英特尔计划在 2024 年或者 2025 年推出 Lunar Lake,应该使用英特尔 18A 工艺节点。MLID 此前表示 Lunar La

关键字:

英特尔 CPU

Arm 推出全新 Arm IP Explorer 平台,该平台是一套由 Arm 提供的云平台服务,旨在为基于 Arm 架构设计系统的硬件工程师与 SoC 架构师,加速其 IP 选择和 SoC 设计,为 IP 选择流程带来跃阶式的效率提升,进而有效提高其开发和生产效率。为了加快产品推向市场,抢占商机,能在 SoC 设计流程的任一环节中提速都至关重要。Arm全新推出的 Arm IP Explorer 在针对用户选择 IP 的痛点进行流程优化,通过探索、设计和分享三方面的多样功能达到效率提升。· &n

关键字:

Arm IP Explorer

IT之家 7 月 18 日消息,国外科技媒体 Igor's LAB 日前爆料,Arrow Lake-S 将采用酷睿 Ultra 品牌,CPU 提升可达 21%,新架构的核显性能也会翻倍。Arrow Lake-S 旗舰型号也是 8 大核 + 16 小核的设计,与当前旗舰 i9-13900K 相同,此前消息称还有 8+32 核心配置的型号。在最新报道中,详细披露了英特尔 LGA 1851 插槽的全部细节,IT之家在此附上链接,感兴趣的用户可以深入阅读。英特尔 LGA 1851 插槽整体上接近

关键字:

英特尔 CPU

近日,有消息称三星的新款芯片Exynos 2400 SoC将拥有10个CPU核心,其GPU基准测试部分得分甚至超过了骁龙8 Gen 3。然而,三星Exynos 2400 SoC的最终配置和封装信息目前仍未确定,三星正在权衡SoC的选择,但预计该芯片将在明年的三星旗舰Galaxy S24系列中亮相。 虽然Exynos 2400 SoC将拥有10个CPU核心,但这10个核心并不会同时运行,芯片将根据每个任务的需要,调度所需的核心数量。此外,最初的传言称Exynos 2400将采用Fo-WLP或Fan-out晶

关键字:

三星 Exynos 2400 CPU 8 Gen3

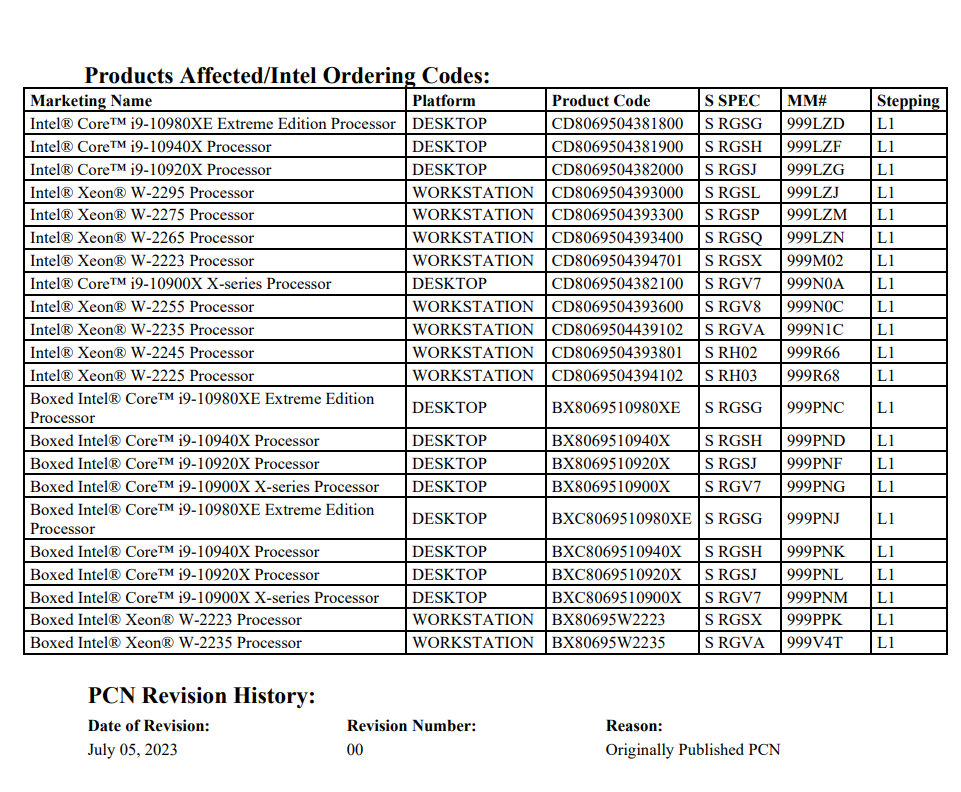

IT之家 7 月 7 日消息,由于来自 AMD EPYC Rome 系列的激烈竞争,英特尔此前停产了部分 Cascade Lake Xeon 处理器,不过还有许多 Cascade Lake 型号幸免于难。而现在,英特尔决定砍掉部分剩余的“幸存者”。英特尔于 2019 年推出 Cascade Lake 来取代 Skylake 处理器,采用 14nm 工艺制造,包括用于 HEDT 的 Cascade Lake-X、用于工作站的 Cascade Lake-W 以及用于服务器的 Cascade Lake

关键字:

英特尔 CPU

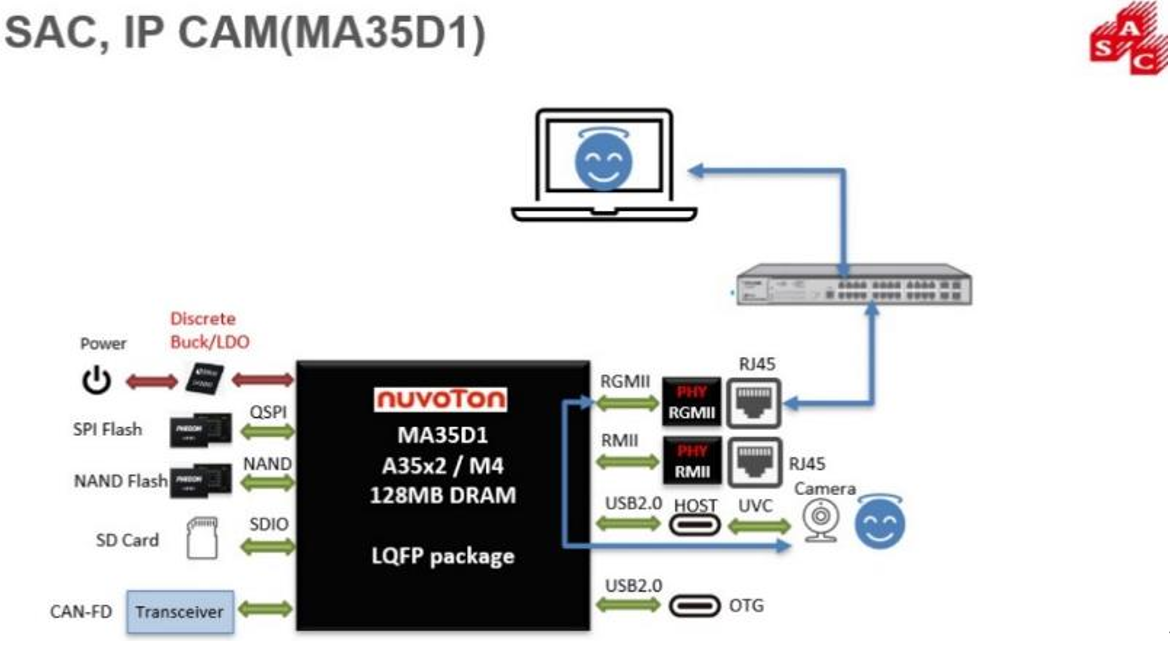

2023年7月6日,致力于亚太地区市场的国际领先半导体元器件分销商---大联大控股宣布,其旗下品佳推出基于芯唐科技(Nuvoton)MA35D1芯片的IP CAM方案。 图示1-

关键字:

大联大品佳 芯唐 IP CAM

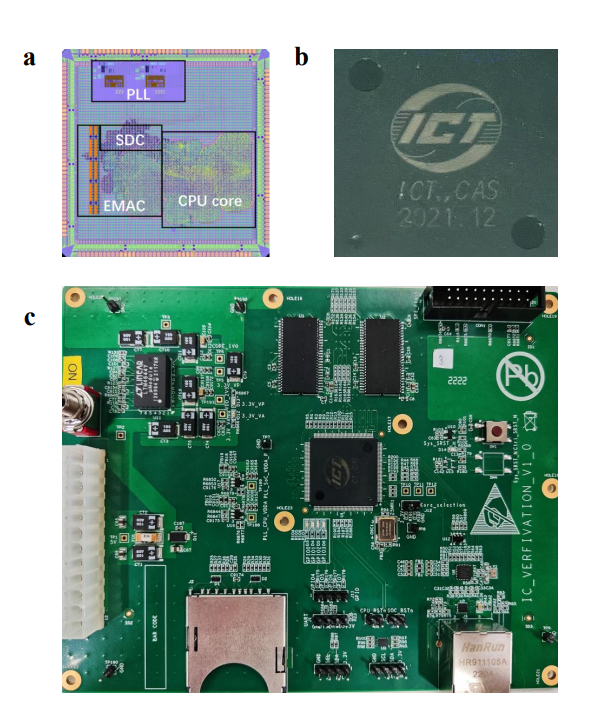

IT之家 6 月 30 日消息,据《半导体产业纵横》报道,中科院计算所等机构用 AI 技术设计出了世界上首个无人工干预、全自动生成的 CPU 芯片 —— 启蒙 1 号。该 CPU 基于 RISC-V 的 32 位架构,其相比于 GPT-4 目前能够设计的电路规模大 4000 倍,性能与 Intel 486 系列 CPU 相当,可运行 Linux 操作系统。▲ 图源中科院计算所论文这是全球首个无人工干预、全自动生成的 CPU 芯片,65nm 工艺,频率达到了 300MHz,相关研究论文已经在今年

关键字:

RISC-V CPU AI

摘要:● 新思科技接口IP适用于USB、PCI Express、112G以太网、UCIe、LPDDR、DDR、MIPI等广泛使用的协议中,并在三星工艺中实现高性能和低延迟● 新思科技基础IP,包括逻辑库、嵌入式存储器、TCAM和GPIO,可以在各先进节点上提供行业领先的功耗、性能和面积(PPA)● 新思科技车规级IP集成到三星的工艺中,有助于确保ADAS、动力总成和雷达SoC的长期运行并提高可靠性● 三星工艺中

关键字:

新思科技 三星 IP SoC设计

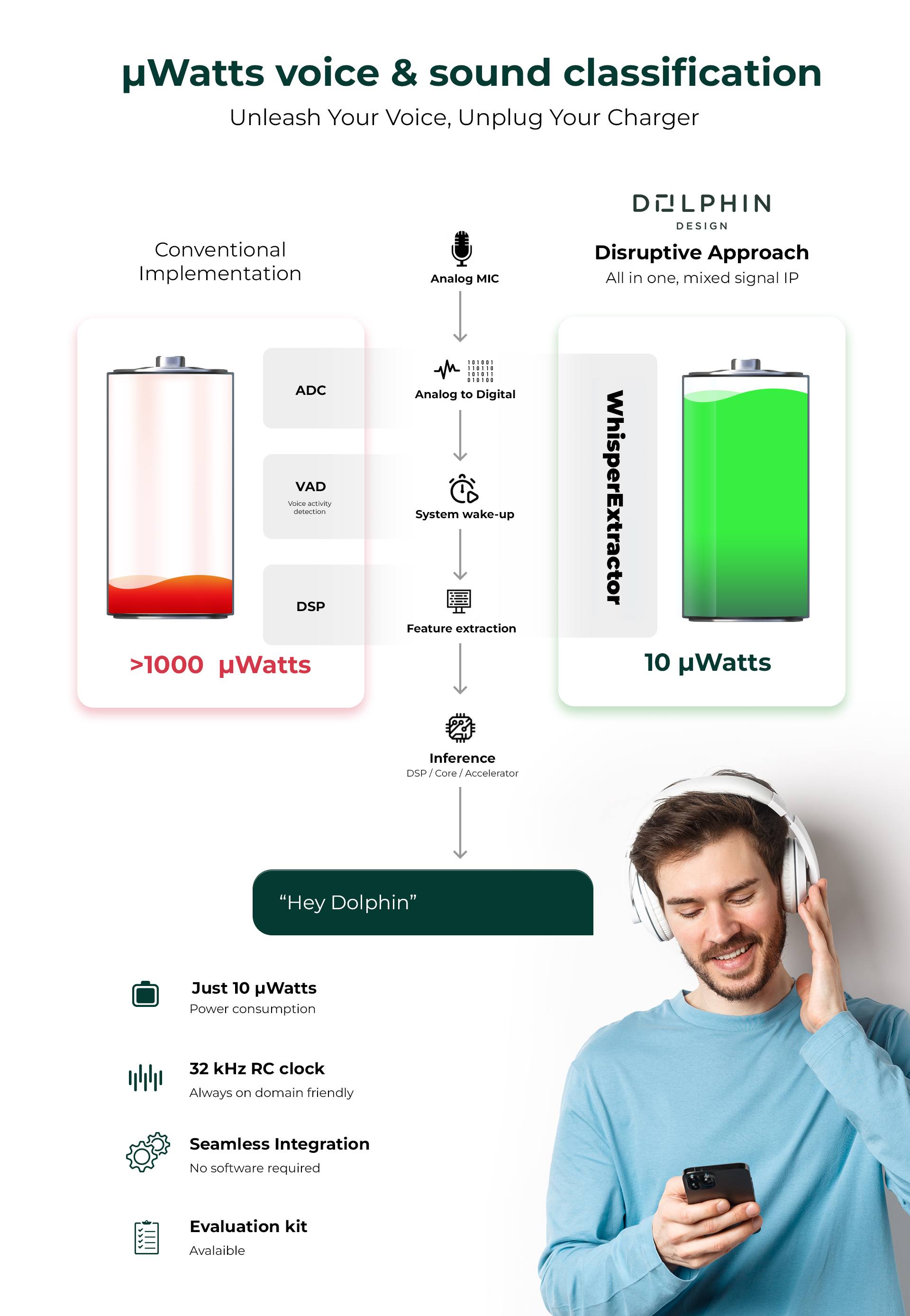

Dolphin Design是提供电源管理、音频和处理器以及ASIC设计服务的半导体IP解决方案的领导者,今天宣布推出WhisperExtractor,这是一个改变游戏规则的混合信号IP,用于支持语音和音频的SoC。WhisperExtractor IP能够以µW级别的功耗实现语音和声音分类,为突破性的在线语音用户界面和在线声音检测铺平道路。该IP增强了旨在实现关键词识别(KWS)、自动语音识别(ASR)、自然语言处理(NLP)或智能安全摄像头等电池供电的高能效声音分类应用。WhisperExtracto

关键字:

Dolphin Design 声音分类 IP

2023年6月28日,格勒诺布尔。Dolphin Design是提供电源管理、音频和处理器以及ASIC设计服务的半导体IP解决方案的领导者,今天宣布推出WhisperExtractor,这是一个改变游戏规则的混合信号IP,用于支持语音和音频的SoC。WhisperExtractor IP能够以µW级别的功耗实现语音和声音分类,为突破性的在线语音用户界面和在线声音检测铺平道路。该IP增强了旨在实现关键词识别(KWS)、自动语音识别(ASR)、自然语言处理(NLP)或智能安全摄像头等电池供电的高能效声音分类应

关键字:

Dolphin Design 声音分类 IP

全球领先的无线连接和智能感知技术及共创解决方案的授权许可厂商CEVA, Inc.(纳斯达克股票代码:CEVA)参加2023年6月28至30日在上海举办的世界移动通信大会。在这次展会上,CEVA团队将与SoC和OEM客户面对面沟通交流,探讨最新的技术创新,并介绍如何充分利用CEVA IP开发无线连接和智能感知应用以实现产品设计目标。 CEVA将在行政会议室展示用于边缘AI、5G、计算机视觉、空间音频(spatial-audio)和物联网连接的最新解决方案,包括: ● 边缘AI推

关键字:

CEVA 上海世界移动通信大会 IP

IT之家 6 月 8 日消息,英特尔即将在今年晚些时候发布新一代处理器,其中包括 13代酷睿 Raptor Lake 的 Refresh 改进版以及全新的 Meteor Lake 处理器。据推特用户 harukaze5719 爆料,RPL-R 处理器的桌面版、H / HX、P 系列将被称为 14 代酷睿,U / Y 系列仍被称为 13代酷睿。MTL 采用了全新的命名方式,可能不会列入 XX 代酷睿的体系。据IT之家早前的报道,MTL 系列处理器已经曝光的型号有 Ultra 5

关键字:

英特尔 CPU

cpu ip介绍

您好,目前还没有人创建词条cpu ip!

欢迎您创建该词条,阐述对cpu ip的理解,并与今后在此搜索cpu ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473