cadence.spb.15.2. 文章

最新资讯

- 2011年10月5日— 全球电子设计创新领先企业Cadence 设计系统公司 (NASDAQ: CDNS),今天宣布顶尖的模拟/混合信号半导体应用晶圆厂X-FAB,已认证Cadence物理验证系统用于其大多数工艺技术。晶圆厂的认证意味着X-FAB已在其所有工艺节点中审核认可了Cadence物理实现系统的硅精确性,混合信号客户可利用其与Cadence Virtuoso和Encounter流程的紧密结合获得新功能与效率优势。

- 关键字:

Cadence 晶圆

- 2011年9月19日 — 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),今日宣布Giantec Semiconductor Corp.已采用Cadence Virtuoso 统一定制/模拟(IC6.1)以及Encounter 统一数字流程生产其混合信号芯片。Giantec最近采用Cadence软件设计并成功流片了一款用于低功耗微控制器的存储器产品,这款低功耗微控制器应用于智能卡、智能电表和消费电子产品。使用Cadence Virtuoso统一定制/模拟流程开发其混合信号

- 关键字:

Cadence 微控制器

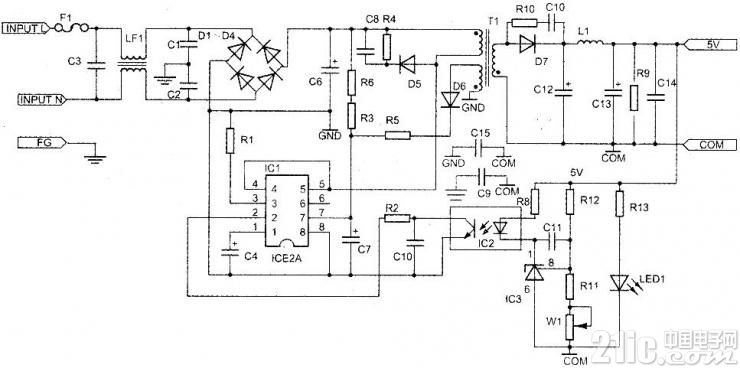

- 美国加利福尼亚州圣何塞,2011年9月6日讯 – 用于LED照明的高压集成电路业界的领导者Power Integrations公司(纳斯达克股票代号:POWI)今日发布一份新的参考设计(DER-281),详细介绍一款能效高达85%的15 W PAR38筒灯驱动器的设计方法,新设计无需使用不可靠的高压大容量电解电容即可实现无闪烁调光。这种创新的调光设计采用了Power Integrations广受欢迎的LinkSwitch-PH系列LED驱动器IC之一LNK405EG,在不需要牺牲可靠性和效

- 关键字:

PI 驱动器 15 W PAR38 LED

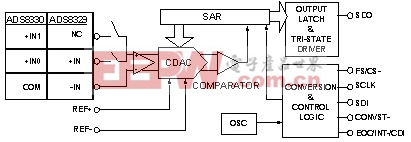

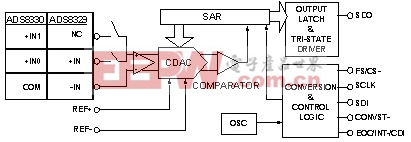

- 今年年初 TI 推出的两款模数转换器 (ADC) ADS8329 和 ADS8330 向世人展现了一个低功耗、高速和高性能的独特组合。该组合使其成为诸多应用的理想选择,例如:通信、医疗仪器、自动测试设备、数据采集系统或工业过程控

- 关键字:

模数 转换器 1MSPS 16位 15.5mW 功耗

- 1 引言 随着人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快.相应的高速PCB的应用也越来越广,设计也越来越复杂.高速电路有两个方面的含义:一是频率高,通常认为数字电路的频率达到或是超过45MHz

- 关键字:

设计 PCB 高速 Cadence 基于

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS) ,宣布推出28纳米的可靠数字端到端流程,推动千兆门/千兆赫系统级芯片(SoC)设计,在性能与上市时间方面都有着明显的优势。在Cadence的硅实现方法的驱动下,在统一化设计、实现与验证流程中,通过技术集成和对核心架构与算法大幅改进,基于Encounter的全新流程提供了更快、更具决定性的途径实现千兆门/千兆赫硅片。

- 关键字:

Cadence 28纳米

- 全球电子设计创新领先企业Cadence设计系统公司,宣布推出28纳米的可靠数字端到端流程,推动千兆门/千兆赫系统级芯片(SoC)设计,在性能与上市时间方面都有着明显的优势。在Cadence的硅实现方法的驱动下,在统一化设计、实现与验证流程中,通过技术集成和对核心架构与算法大幅改进,基于Encounter的全新流程提供了更快、更具决定性的途径实现千兆门/千兆赫硅片。通过与Cadence的模拟/混合信号与硅/封装协同设计领域的无缝综合,新的数字28纳米流程让设计师能够全局考虑整个芯片流程,在高性能、低功耗

- 关键字:

Cadence 28纳米

- Cadence端到端芯片实现流程帮助基带芯片生产商提高生产力、改进预测准确性以及缩短产品上市时间

全球领先的电子设计创新企业Cadence设计系统公司,宣布总部位于上海的无线通信基带和RF处理器解决方案领先供应商展讯通信有限公司已将其芯片设计流程成功迁移到Cadence Silicon Realization,并实现了其首款40纳米低功耗GSM/GPRS/EDGE/TD-SCDMA/HSPA商用无线通信

- 关键字:

展讯 40纳米 Cadence EDA

- 全球电子设计创新领先企业Cadence设计系统公司,今天宣布在帮助ASIC与FPGA设计者们提高验证效率方面取得最新重大进展。加上对最新Accellera Universal Verification Methodology (UVM) 1.0业界标准的全面支持,600多种新功能扩展了指标驱动型验证(MDV)的范围,帮助工程师实现更快、更全面的验证闭合与硅实现。

- 关键字:

Cadence FPGA

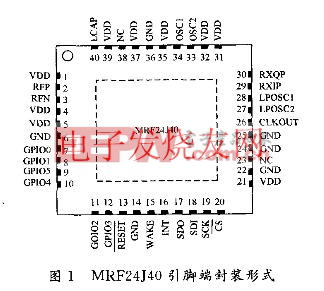

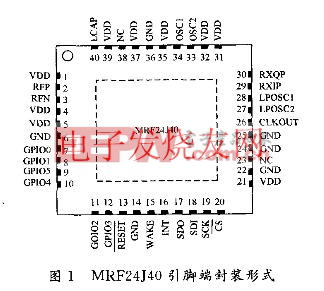

- 1 IEEE802.15.4收发器芯片MRF24J40 IEEE802.15.4 无线收发器MRF24J40芯片内部包含有SPI接口、控制寄存器、MAC模块、PHY驱动器四个主要的功能模块,支持 IEEE802.15.4,MiWiTM,ZigBee等协议,工作在2.405~2.48

- 关键字:

收发器 电路设计 无线 IEEE802.15.4 MRF24J40 基于

- 全球电子设计创新领先企业Cadence设计系统公司,今天宣布中国最大的半导体晶圆厂中芯国际集成电路制造有限公司,已经将Cadence® Silicon Realization产品作为其65纳米参考流程4.1版本(Reference Flow 4.1)可制造性设计(DFM)以及低功耗技术的核心。以Cadence Encounter Digital Implementation System为基础,两家公司合作为65纳米系统级芯片(SoC)设计提供了一个完整的端到端的Silicon Realiza

- 关键字:

中芯国际 Cadence 65纳米

cadence.spb.15.2.介绍

您好,目前还没有人创建词条cadence.spb.15.2.!

欢迎您创建该词条,阐述对cadence.spb.15.2.的理解,并与今后在此搜索cadence.spb.15.2.的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473