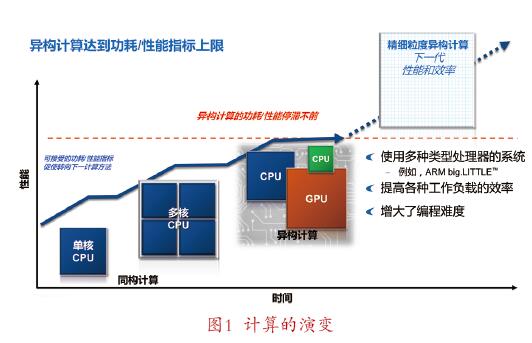

不久前,Altera公司在深圳举办了Altera SoC开发者论坛(ASDF)。此活动一共在全球三地举办—美国硅谷、德国法兰克福和中国深圳。会上,合作伙伴、开发者和工程师汇聚一堂,交流基于ARM的SoC FPGA应用,以及探讨下一代精细粒度异构计算及产品。Altera SoC已有二百多电机案例 Altera嵌入式处理营销资深总监Chris Balough称,Altera SoC开发已有5年。Intel即将收购Altera,Intel已承诺持续支持Altera发展ARM处理器及下一代FPGA。原因之一

关键字:

Altera ASDF 201512

山东高云半导体科技有限公司(以下简称“高云半导体”今日宣布,在山东省国产IP软核平台上发布三个IP软核参考设计,分别是:I2C总线、SPI、UART,作为星核计划取得的初步成果,这三个软核在工业控制、系统调试以及嵌入式开发中具有非常广泛的应用。 “山东省国产IP软核平台由山东信息通信研究院、高云半导体共同发起,致力于打造国内首家国产IP软核资源库”,山东高云半导体科技有限公司总经理梁岳峰先生表示,“该平台以山东信息通信研究院的集成电路设计测试平台、高云半导体星核计划为依托,本着开放、资源共享的原则,

关键字:

高云 半导体 FPGA

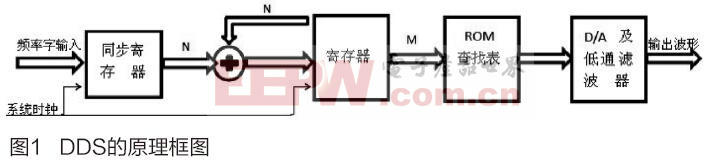

最近接了一个项目吧,是我们学校物理院院长带的研究生搞的,小墨有幸跟他们合作,负责FPGA方面的工作,完成后据说还会申请国家专利,具体到什么时候完成,那可能就是猴年马月了,或者说我已经不在学校了。从今天开始,小墨将开始接触赛灵思公司的FPGA(老师提供的平台),用到的当然是SOPC。其实做做项目也好,让自己锻炼一下,我也好久没有做大一点的项目了,对我来说也是一个机会吧。 信号发生器这个东西相信大家都知道,关于基于DDS信号发生器的技术文档网上也多的是,但是我还是想写一下这部分的教学,因为从我自身的学习

关键字:

FPGA SOPC

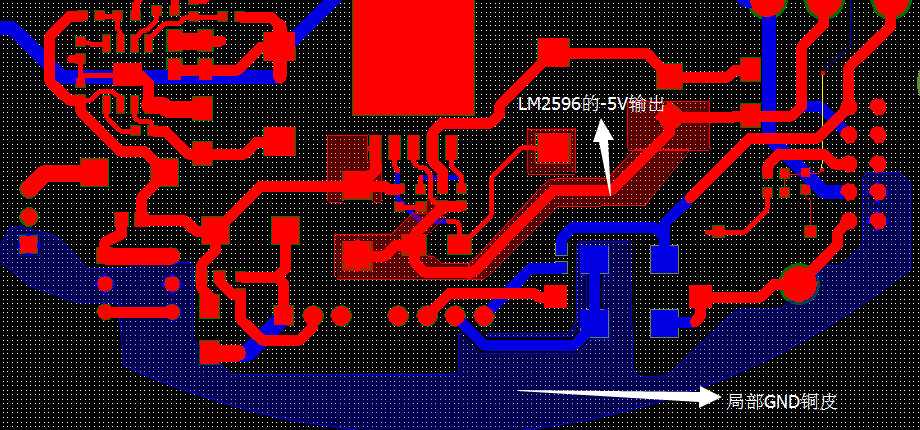

想要成为一名硬件工程师首先必须掌握的就是PCB的设计与绘制,这里我们为大家整理了几条设计技巧。 1、如果设计的电路系统中包含FPGA器件,则在绘制原理图前必需使用Quartus II软件对管脚分配进行验证。(FPGA中某些特殊的管脚是不能用作普通IO的)。 2、4层板从上到下依次为:信号平面层、地、电源、信号平面层;6层板从上到下依次为:信号平面层、地、信号内电层、信号内电层、电源、信号平面层。6层以上板(优点是:防干扰辐射),优先选择内电层走线,走不开选择平面层,禁止从地或电源层走线(原因:会分

关键字:

PCB FPGA

摘要:在科技飞速发展的今天,各种自动化仪器及自动控制都离不开信号采集,而且要采集的信号越来越快,精度要求也越来越高。如何简单快速的让系统集成这项功能呢?

1、ZSDA1000的基本介绍 ZDS1000是ZLG致远电子开发的高速信号数据采集模块,模块通过PCI Express2.0接口与主机端连接,350M带宽,1GSa/s的采样速率。用户只需要通过动态链接库文件就可以轻松控制模块进行数据采集和数据处理。可用于质谱分析、雷达信号捕捉、材料分析等场

关键字:

FPGA ZSDA1000

本文利用直接数字合成技术通过一款FPGA可编程逻辑芯片实现函数信号发生器的研制,该信号发生器是以Altera公司生产的EP4CE6F17C8芯片为设计载体,通过DDS技术实现两路同步信号输出。通过软件Quartus-II12.0和Nios-II 12.0开发环境编程,实现多种波形信号输出,信号具有高精度的频率分辨率能力,最高可达36位。最后通过实验输出的波形信号符合标准。

关键字:

直接数字合成技术 FPGA 信号发生器 Quartus-II 201512

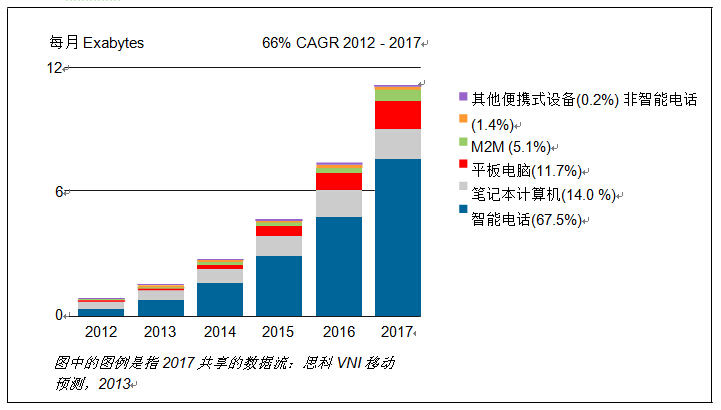

本白皮书介绍为什么电信带宽和基础设施促进了FPGA功能的增强,以及ASIC和ASSP面临的商业挑战,可编程逻辑器件(PLD)定制方法是怎样支持FPGA功能的跨越式发展。本文还简要介绍了下一代FPGA和SoC系列品。 引言 最新发布的FPGA是硬件规划人员、软件开发人员和系统设计人员实现其下一代产品目标的关键支撑因素。大量的电信基础设施成指数增长的带宽需求以及各行业使用这些带宽的需求使得现有硬件和软件解决方案很难满足性能要求,也难以达到成本和功耗目标。ASIC、ASSP和独立处理器遇到了发展瓶颈,P

关键字:

FPGA SoC

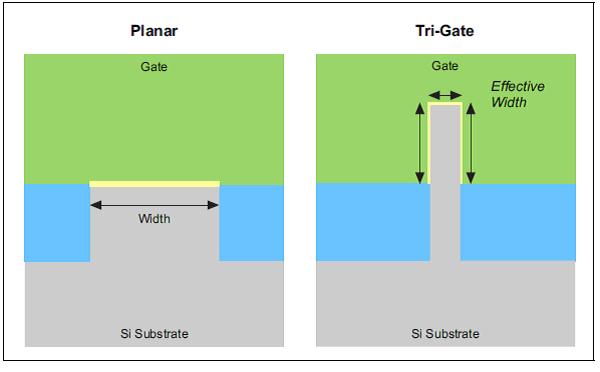

引言 2013年2月,Altera公司与Intel公司共同宣布了Altera下一代最高性能FPGA产品的生产将独家采用Intel的14nm 3D Tri-Gate(三栅极)晶体管技术。这使得Altera成为当前采用最先进、最高性能半导体技术的独家专业FPGA供应商。本文介绍了三栅极及相关技术的历史与现状,以便了解三栅极技术对高性能FPGA性能的影响,以及其在数字电路速度、功率以及生产方面有何种程度的优势。 晶体管设计的背景 1947年,贝尔实验室展示了第一支晶体管,采用的是锗

关键字:

Altera FPGA

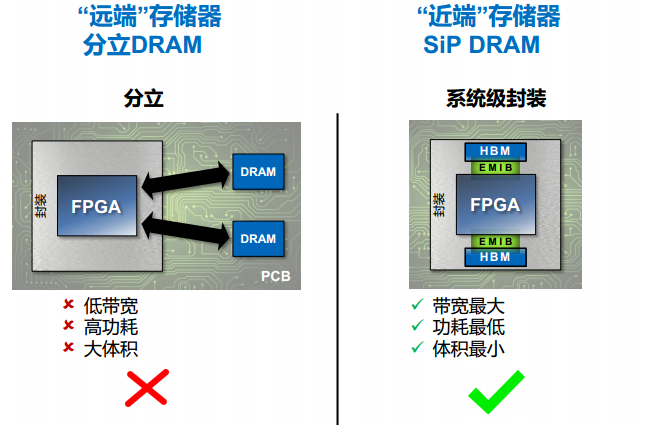

计划于2017年出货的最新的Stratix 10 DRAM SiP产品将采用存储器厂商现代公司的HBM DRAM内存,通过英特尔先进的嵌入式多裸片互连桥接(EMIB)技术,将FPGA、MCU、DSP以及DRAM等其他功能模块集成在2.5D的SiP封装内,实现一个异构多核的SoC FPGA产品。相对于目前的分立DRAM解决方案,Stratix 10 DRAM SiP的存储器带宽提高了10倍。 伴随着客户对系统的要求不断攀升

关键字:

Altera Stratix

Altera公司今天公开业界第一款异构系统级封装(SiP,System-in-Package)器件,集成了来自SK Hynix的堆叠宽带存储器(HBM2)以及高性能Stratix® 10 FPGA和SoC。Stratix 10 DRAM SiP代表了新一类器件,其特殊的体系结构设计满足了高性能系统对存储器带宽最严格的要求。

数据中心、广播、固网和高性能计算等系统要处理的数据量不断攀升,需要的带宽非常高。相对于目前的分立DRAM解决方案,Stratix 10 DRAM SiP的存储器带宽提

关键字:

Altera DRAM

Altera公司今天宣布,开始提供面向Nios® II嵌入式处理器的Altera®功能安全锁步解决方案,这一解决方案降低了设计周期风险,帮助系统设计人员简化工业和汽车安全应用的认证。Altera与意大利比萨的功能安全领先供应商YOGITECH联合开发的锁步解决方案采用了Altera FPGA、SoC,认证工具流程,以及YOGITECH的知识产权(IP)内核。这一解决方案帮助客户在Altera FPGA中轻松实现SIL3安全设计,包括低成本Cyclone® V&n

关键字:

Altera FPGA

面对清华紫光集团董事长赵伟国再次放话,将先把收购目光集中在美国半导体产业的说法,日前台系IC设计公司均表达不意外,毕竟台湾政府目前尚未通过相关法令限制,加上相关配套措施还需产官学界互相讨论,与其现在买市值不大的台湾IC设计公司,对清华紫光集团并无法产生立即性的帮助。

产业界人士指出,以清华紫光的大陆内需市场色彩,加上先前出手目标多锁定具备一定程度寡占特性的产业来看,全球三强鼎立的EDA市场、绘图芯片与FPGA产业,或许是清华紫光集团在谈判桌上的下一个目标。

确实从清华紫光收购动作一路多锁定

关键字:

紫光 FPGA

Altera公司(Nasdaq)公开业界第一款异构系统级封装(SiP,System-in-Package)器件,集成了来自SK Hynix的堆叠宽带存储器(HBM2)以及高性能Stratix® 10 FPGA和SoC。Stratix 10 DRAM SiP代表了新一类器件,其特殊的体系结构设计满足了高性能系统对存储器带宽最严格的要求。

数据中心、广播、固网和高性能计算等系统要处理的数据量不断攀升,需要的带宽非常高。相对于目前的分立DRAM解决方案,Stratix 10 DRAM SiP的

关键字:

Altera FPGA

Altera公司今天公开业界第一款异构系统级封装(SiP,System-in-Package)器件,集成了来自SK Hynix的堆叠宽带存储器(HBM2)以及高性能Stratix® 10 FPGA和SoC。Stratix 10 DRAM SiP代表了新一类器件,其特殊的体系结构设计满足了高性能系统对存储器带宽最严格的要求。

数据中心、广播、固网和高性能计算等系统要处理的数据量不断攀升,需要的带宽非常高。相对于目前的分立DRAM解决方案,Stratix 10 DRAM SiP的存储器带宽提

关键字:

Altera FPGA

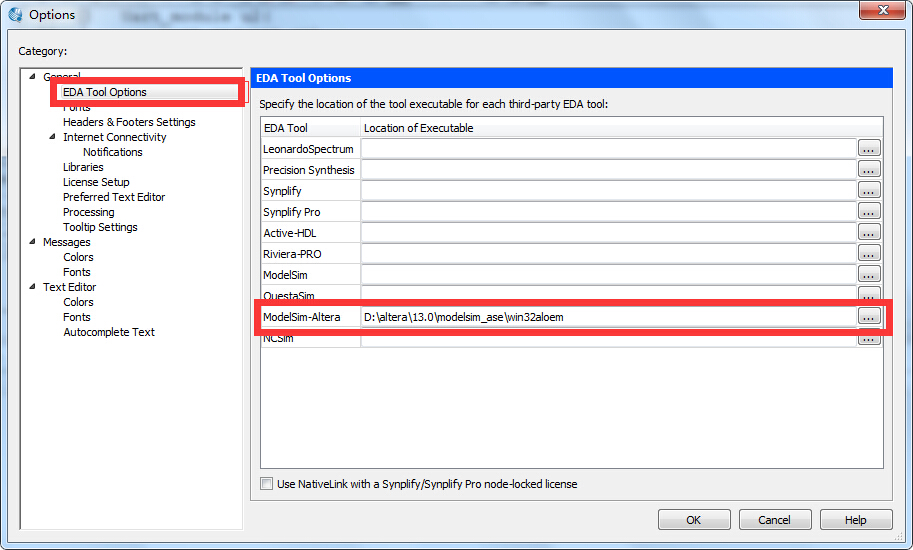

以上为小梅哥为了对特权同学的串口收发模块进行测试所展开的部分工作,到这里,仿真测试所需要的准备工作我们就做好了,接下来将实际进行仿真,通过仿真来分析该模块的性能。 这里极力推荐大家使用modelsim进行仿真,因为quartusII自带的仿真工具灵活性和功能都赶modelsim相差甚远。Modelsim作为一款强大的仿真软件,在业界被广泛使用。同时,modelsim针对不同的EDA厂家,也推出了OEM版本,modelsim-altera就是为Altera公司开发的OEM版本,此版本针对Altera公

关键字:

FPGA 串口调试

altera-fpga介绍

您好,目前还没有人创建词条altera-fpga!

欢迎您创建该词条,阐述对altera-fpga的理解,并与今后在此搜索altera-fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473