亲自实践项目:(下篇) 系统性能加速的自动化

自动化如何使没有硬件背景的设计师能实现定制硬件的加速。

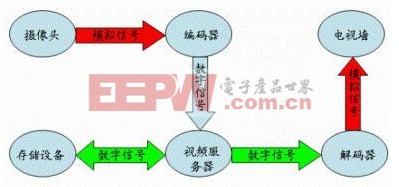

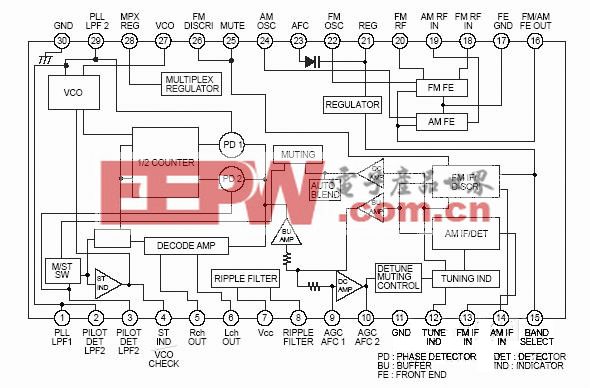

越来越多的产品正在使算法模型和软件代码转换成硬件这一过程自动化,从而使没有具体硬件背景的设计师能够实现定制硬件加速。这些工具并不改变设计或工具流程,但可使这一流程中的一些手工步骤自动化(图 1)。这些工具要达到的目标是:要比其他方法缩短实现一项设计所花的时间,使设计师能探索更多的设计配置,使整个设计小组在完成某个项目期间能依靠单独资源工作,使用自动的“按结构校正”方法来提高流程可靠性,并确保验证流程与原始规范相联系。

正如这篇连载文章的上篇(见本刊2005年第2期 )所描述的,把定制硬件作为加速软件性能的指令或协处理器)来创造的各种可选方案正在演进之中。不过,上篇描述的过程假设:硬件工程师以人工方法把软件转换成硬件。虽然各种新型工具能使这一过程自动化,但大多数根据软件描述生成 RTL(寄存器传输语言)的工具都要求设计师至少了解一些要考虑的硬件因 素(见附文《把软件移植到硬件》)。

素(见附文《把软件移植到硬件》)。

根据某一算法规范或软件规范创建硬件并非没有挑战。设计师把某种算法作为软件来探索和实现所需要的技能,不同于用 FPGA 或 ASIC 来实现该算法所需的技能。软件设计师很少需要考虑系统时钟的偏斜、总线的容量和加载、模拟信号的处理和特性、温度、功耗以及电磁干扰,而所有这些都会影响硬件设计师优化设计的方法。软件采用一种顺序计算模型,而硬件一般处理设计师以很高的并行度来实现的状态机和组合逻辑。

传统的 EDA 工具处理的是如何在更高的程度上对硬件进行抽象,以提高设计师的工作效率。根据软件代码自动生成 RTL 的各种工具都有一个不同的重点。据 CriticalBlue 公司首席执行官 David Stewart 说:“挑战在于如何抽象各种软件概念,以便工具能把它们作为硬件来实现。”这些工具是供没有硬件背景的设计师而不是供精通 Verilog 或 VHDL 的硬件设计师使用的。这些工具允许在整个设计过程中坚持使用软件开发方法。它们使算法模型或软件代码在整个项目期间仍然是一个绝佳的资源,所以,对它所做的种种修改就能迅速、可靠、自动地传递到下游的动作中。

设计师在算法级要比在硬件级更容易了解总体情况。与 RTL 级仿真器相比,算法仿真器和软件仿真器能在宽得多的时间段内描述相关系统行为的特性,因此设计师就能探索并勾勒出更多的使用环境。鉴别高级别行为优化所带来的总系统性能提高要比鉴别低级别硬件优化大得多。软件转换成硬件这一过程实现自动化,也使设计师能探索更多其它的芯片实现方法,这是因为这些工具可简化这种转换工作,并可减少对设计修改所造成影响进行评估的时间。

这些工具通常通过对资源的报告、调度和显式映射,支持对处理速度和面积之间的折衷方案的分析和执行。除了生成RTL代码以外,这些工具还能在验证过程期间节省设计师的时间,这是因为它们能自动生成的测试台可利用来自各种算法探索工具的促进因素。这些工具几乎都不是独立的;当它们针对特定的FPGA器件或工艺技术时,便可与芯片制造商的工具接口,或直接集成到这些工具中。

正是因为一些工具能根据软件自动生成 RTL 代码并不意味着把它们用于所有代码是合理的。一般来说,与软件相比,硬件实现方法并不能以更好的成本和性能指标来执行复杂的顺序操作。适合转换成硬件的候选算法或功能有:能执行并行操作,并能受益于运行多个实例的算法或功能;能利用非标准的数据位宽度的算法或功能;能流水线操作的算法或功能;能完成那些执行时间比数据传输时间大得不成比例的数据处理的算法或功能。

从软件到 RTL

AccelChip 公司提供各种算法综合和验证工具及服务,可用来支持适用于FPGA、结构化 ASIC、普通 ASIC 的自顶向下 DSP 设计。今年,该公司推出了 AccelChip DSP Synthesis 工具,这是 AccelFPGA 的第二代替代产品,能直接根据MathWorks公司的 Matlab工具(用于DSP算法开发、数据可视化、数据分析)自动生成可综合的RTL模型。该公司还推出了 AccelWare,这是一种参数化DSP IP(知识产权)构件块,用以完成普通 Matlab工具箱功能。AccelWare块使用与Matlab功能和Simulink块相同的参数,并允许设师规定诸如定时等各种实现参数,以达到设计目标。AccelChip DSP Synthesis工具可为 整个算法生成RTL,其中包括 AccelWare 块。

AccelChip公司 的各种工具能使 Matlab工具在整个设计过程中仍然是绝佳的资源,这全在于它们能通过 MathWorks公司的Simulink接口支持系统级验证,并能集成到Synopsys公司的ASIC和Xilinx公司的System Generation工具流程中。AutoQuantizer工具能利用原始的浮点源和设计模型来确定每个变量的动态范围,由此使浮点模型变成定点设计这种转换自动化。AccelChip公司 的各种工具产生根据位真实的、周期精确的定点Matlab模型生成Simulink S 函数所必需的文件。AccelChip DSP Synthesis工具自动生成设计师用来验证布局后定点设计的仿真测试台。

Synplicity 公司的综合、验证和物理实现三种软件工具都是以实现FPGA、结构化 ASIC、平台 ASIC、单元基 ASIC、COT(客户自有的工具) ASIC 为目标的。该公司今年推出的Synplify DSP,能根据 Matlab 模型和 Simulink 模型生成可马上综合的 RTL 代码。Synplify DSP 工具使用系统级重定时等算法,以便在生成 RTL 之前在系统级优化 Simulink 模型,从而提高 DSP 实现性能。设计师只要根据一个单通道规范自动生成的一个多通道系统,就能对线程容量进行模拟分析。该工具能在规定的性能预算内共享器件上的资源,如乘法器,并且它支持在实现之前进行针对面积和性能的折衷分析,从而减少设计迭代。

评论