系统LSI的低功耗设计

当前,LSI遵循按比例缩放的规则,已能实现超过GHz的工作频率,一个芯片上已集成有数千万个晶体管,LSI已从过去的元器件型变到了系统LSI。在芯片面积与工作频率一定的条件下,施行器件的按比例缩放,功率与缩放率达到近似于反比地降低。但是,在近来的系统LSI中,多媒体、网络及声音处理等却要求超过器件按比例缩放的处理性能,有工作频率提高、芯片面积增大而功耗增加的趋势。

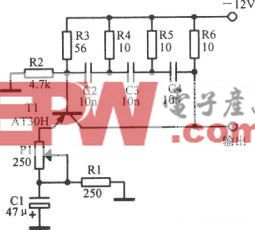

本文引用地址:https://www.eepw.com.cn/article/3013.htm图1示出微处理器的功耗趋势,曾经每芯片的功耗约为100W,而这将超过空气冷却下陶瓷封装的散热限制,而且还面临电源线电压下降及CMOS LSI可靠性降低等问题。不仅是高性能MPU和多媒体DSP,即使机顶盒、彩电等家电设备,因成本考虑必须塑料封装,功耗也受到限制。此外,在市场迅速扩大的PDA、W-CDMA等移动信息终端方面,基于电池的长寿命考虑,低功耗是必需的。因此,系统LSI因高性能及细微化引起的电路大规模化,低功耗技术成了必需的技术。

在CMOS电路中,一般消耗功率与延迟时间的近似表达式由下式表示:

p=a.f.CL.Vs.VDD+a.ISC.Δtsc.VDD.f+IleakVDD (1)

式中α为转换概率,CL为负载电容,Vs为信号幅度,VDD为电源电压,ISC为贯通电流的平均值,Δtsc为贯通电流流过的时间,f为时钟频率,Ileak为漏泄电流。式中第一项为负载电容充放电所需的功率,Vs与VDD通常相等,故与电源电压的2次方成比例,第二项是门转换时流过的贯动电池产生的功率,因输入信号比输出信号变化快,故其值很小,在电路设计时按输入信号与输出信号的迁移时间大体相等考虑,其贯通电流产生的功率可限定为第1项的大约10%。第3项是恒定流过电源与密封罩的漏泄电流产生的功率。

由于比起第2项功率来说第1项功率占支配地位,工作功率Pa可近似为:Pa=α.f.CL.VS.VDD。因此,降低工作功率Pa的技术关键是减小转换概率α、负载电容CL、时钟频率f的低频化、信号幅度VS和电源电压VDD的低压化。

此外,待机功率PS因是晶体管漏泄电流产生的功率,故为第三项。漏泄电流主要是亚阈值漏电流、区域间隧道漏电流(GIDL:栅极感生的漏极漏电流)和栅极隧道漏电流。

亚阈值漏电流为晶体管断路状态时流过漏极与源极间的电流,对于0.1V的低阈值化约增大1个数量级。区域间隧道漏电流是流过漏极与基板间的漏电流,对于栅极氧化膜及漏极扩散层界面的电场强度的增大呈指数函数增大。此外,栅极隧道漏电流在晶体管导通状态时在通道与栅极间,在断路状态时在漏极与源之间流过的漏电流,由于栅极氧化膜的薄化而呈指数函数增大。减小待机功率PS的技术关键在于减小这些漏电流。

作为减小转换概率a的技术,由于时钟系统的功耗大,通常采用通过抑制触发器(FF)的时钟输入,来抑制下级组合电路的转换,使LSI内部的转换概率a降低的栅控时钟方式。这种方式由于需要抑制信号生成的逻辑,为减少其功率消耗,必须把多个FF归组生成抑制信号。

如何降低频率f?由于只降低频率会使工作速度降低,故采用LSI内部的每个功能块分配一个最佳工作频率的方法,使平均功耗降低的工作频率达到最佳分配方式。

减小负载电容CL,不言自明细微化是有效的,但也开始采用了旁路晶体管逻辑电路等非CMOS电路技术。但是,由于设计和验证复杂,必须确定设计工具和设计流程。

通常由于信号幅度VS与电源电压VDD相等,因此,降低VDD对低功耗有2次方的作用。不过,电源电压的降低关系到工作速度的下降,故低压化和并行处理技术一起采用。并行处理技术将流水线划分更细而不致降低吞吐率。此外,还采用对LSI内部的各功能块提供最佳电源电压的多电源技术。最近,在Transmeta的Crusoe及Intel的 Xsale 等芯片中,还采用了对高速处理提高驱动电压和频率,对负载小的处理则降低驱动电压和频率的动态电压/频率控制方法。

LSI由于遵循按比例缩放的原则,在同时达到高速化与低功耗化的同时,还实现了高集成化、大规模化和高功能化。但是,随着细微化带来的低阈值化及栅极氧化膜的薄化,增加了亚阈值漏泄电源和栅极隧道漏泄电流。为此,提出了减小这些漏泄电流而又实现所希望的LSI功能的技术。

对于降低亚阈值漏泄电流的技术,由于提高阈值是有效的,故作为低功耗晶体管可采用比遵循按比例缩放的晶体管阈值略高的设计,并在设计时分别使用高阈值与低阈值两类晶体管,通过减少低阈值晶体管的使用频度而降低亚阈值电流产生的功耗,即所谓双阈值技术。

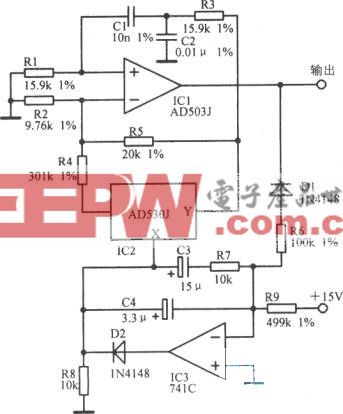

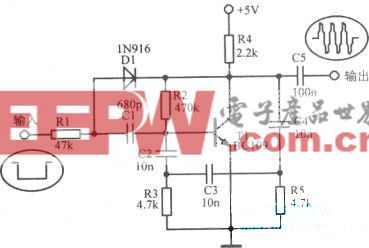

例如,对图2所示电路的严格路径用低阈值晶体管,其它则用高阈值晶体管构成。该技术在高阈值晶体管使用频率高的场合效果很大,但不能减少栅极隧道漏泄电流。此外,迄今提出的电路技术中,大致可分为MT-CMOS(即多阈值CMOS)与VT-CMOS(即可变阈值CMOS)。

MT-CMOS技术如图3所示,在电路与电源线之间插入高阈值晶体管作为电源开关,工作时由低阈值晶体管构成的电路实现高速工作,待机时使高阈值晶体管电源开关处于断路状态,而减小流过电路的亚阈值漏泄电流。该项技术由于待机时电源开关处于断路状态,因不能保持存储在寄存器电路中的数据,故必须采取把数据待存于外部存储器等方法,此外还必须避免插入电源开关带来的面积开销。

VT-CMOS技术如图3(b)所示控制晶体管的基片电位,工作时浅置基片电位,降低晶体管的阈值电压,实现电路的高速工作,待机时深置基片电位,提高晶体管的阈值电压,而减小流过电路的亚阈值漏泄电流。此种方式由于必须把基片与电源线及接地线分开,故需要三重结构及电源电路。此外,如深置基片电位,则GIDL电流增加,反之则总的漏泄电流增加,此其缺点。为此提出了一种技术把电源电压控制与基片偏置控制结合起来,待机时深置基片电位减小亚阈值漏泄电流的同时施以低电源电压,减弱栅极氧化膜与漏极扩散层间的电场来减小GIDL电流。

而减小栅极隧道漏泄电流技术,由于增大栅极氧化膜厚度是有效的,故低功耗晶体管,采用比遵循比例缩放细微化晶体管的栅极氧化膜略厚的晶体管设计,并在设计时分别使用栅极氧化膜厚薄不同的2种晶体管,而尽量减少薄栅极氧化膜晶体管的数量,以降低氧化膜厚度技术。该技术在厚栅极氧化膜晶体管使用频率高的场合是有效的,但由于不能抑制亚阈值电流,为抑制亚阈值电流还必须设定高的阈值。

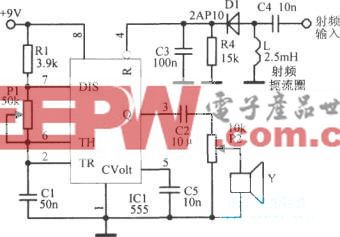

进而又提出了图4所示应用MT-CMOS技术的设计方案。这种方案是把厚栅极氧化膜晶体管串接到电路中,工作时薄栅极氧化膜晶体管构成的电路工作,实现高速工作,待机时让厚栅极氧化膜晶体管导通,而减少栅极隧道漏泄电流。除此之外,由于降低栅极电压,栅极漏泄电流将呈指数减少,工作时使用通常的电源电压,待机时使用低电源电压,此种电源电压控制方式也是有效的。

所谓系统LSI的低功耗设计就是定量减少下式消耗能量的设计。

功耗=工作时功耗+待机时功耗+工作与待机切换功耗 (2)

式中,工作功耗为工作功率Pa×工作时间,待机功耗(即时钟停止时)为待机功率PS×待机时间,工作待机切换功耗是引入MT-CMOS及VT-CMOS时的功耗。

例如,高性能MPU及多媒体DSP等高性能LSI,工作时间比待机时间长,工作能耗占支配地位,漏泄电流产生的功耗可以忽略。因此,为降低能耗采取对每种功能块提供最佳电源电压和频率的多电源、多频率技术是有效的。而为降低工作功耗,根据不同的处理改变电源电压和频率的技术虽有效,但为满足应用的实时要求,必须确定控制电源电压的编辑技术和操作技术。

在便携式设备LSI中,工作时间比待机时间短,待机功耗可能居支配地位,在这种情况下,MT-CMOS及VT-CMOS等降低漏泄电源技术就有效了。不过,只有待机功耗比工作待机切换功耗大的情况才有效。

待机时间比工作时间长且待机功耗居支配地位的LSI中,双阈值、双栅极氧化膜厚器件技术以及MT-CMOS、VT-CMOS等电路技术都有效。而且,漏泄电源可以通过降低电源电压来减少,所以电源电压控制也有效,不过,MT-CMOS及VT-CMOS等电路技术只有在待机功耗大于工作待机切换功耗的情况下才有效。

如上所述,系统LSI虽因芯片规格的不同所采用的技术不一样,但电源电压控制技术都是必不可少的技术。此外,针对系统LSI低功耗化的许多电路技术,其实现并不在于实际的产品中,而在于与设计工具的配合。今后,包含功耗估算工具在内的LSI设计工具及其设计流程的建立仍是课题。

鉴于细微化的进一步发展及CMOS栅极氧化膜的薄化在理论上几乎达到了极限,今后栅极氧化膜必须引入具有高介电常数的绝缘膜。此外,由于芯片中内存所占比例逐年增大,内存单元漏泄电流的影响今后会越来越大。目前用SRAM保存数据的情况下,为减小漏泄电流,不能用MT-CMOS等技术切换电源。所以,在不能抑制内存单元漏泄电源增大的情况下,只能对逻辑电路中的晶体管细微化,内存单元不细微化。因此,如FeRAM及MRAM等非易失性存储器必然成为今后的片上内存。此外,由于工作时亚阈值漏泄电流的影响也不能忽视,其控制也是需要的。虽然本文未能述及,但鉴于负载电容中布线电容占有支配地位,引入Cu布线及低介电常数层间绝缘膜是必不可少的,充分研究这些材料的设计技术也很必要。

此外,芯片上集成的晶体管数量飞速增加,且许多功能块都可做在一枚芯片上,这可以从一个侧面看出,只实施低功耗化难有大的成效,因此,必须既从LSI整体出发也从体系结构、逻辑、电路各方面做起才行。■(绍莹)

评论