基于Zynq的OLED驱动设计

Zynq的硬件系统是指在PL中配置相关外设,挂载到PS中,作为PS部分的外设使用。OLED驱动主要用到6个IO口,在生成硬件系统时,只需要利用Xilinx的嵌入式工具XPS生成最小硬件系统,然后把OLED的相关引脚添加到最小硬件系统中。主要过程如下:

本文引用地址:https://www.eepw.com.cn/article/273002.htm(1)根据芯片型号,根据XPS工具设计流程,生成Zynq的最小硬件系统。

(2)在最小硬件系统中,添加外设IPmy_oled,把OLED的SPI引脚添加到工程中。添加一个6位寄存器,每位和SPI引脚对应。

(3)my_oledIP核逻辑设计主要完成IP核引脚添加、端口映射和用户逻辑功能。首先要对设计的IP核添加引脚,在系统生成的MPD文件中,添加OLED的相关引脚端口和方向信息。

在MPD文件中,在PORT下添加OLED的相关引脚和方向信息,具体代码如下:

PORTDC=“”,DIR=O

PORTRES=“”,DIR=O

PORTSCLK=“”,DIR=O

PORTSDIN=“”,DIR=O

PORTVBAT=“”,DIR=O

PORTVDD=“”,DIR=O

(4)在系统生成的my_oled.vhd文件中,用VHDL语言进行端口设计,主要进行以下两个设计。

声明IP和用户6个信号和电源的端口。代码如下:

DC∶outstd_logic;

RES∶outstd_logic;

SCLK∶outstd_logic;

SDIN∶outstd_logic;

VBAT∶outstd_logic;

VDD∶outstd_logic;

将用户端口和IP核端口进行映射,代码如下:

DC =>DC,

RES =>RES,

SCLK =>SCLK,

SDIN =>SDIN,

VBAT =>VBAT,

VDD =>VDD,

(5)在系统生成的user_logic.v文件中,用Verilog语言进行逻辑设计,实现寄存器和SPI对应端口连接并实时读取,主要代码如下。其中slv_reg0为IP核寄存器,tmp为用户定义临时寄存器,tmp的每一位和IP端口一一对应。实现把slv_reg0寄存器低6位实时传给tmp寄存器,通过对寄存器slv_reg0的写操作达到控制6个引脚的时序。

always@(posedgeBus2IP_Clk)

begin

tmp<=slv_reg0[5:0];

end

4 OLED驱动程序设计

由于ZedBoard开发板上的OLED使用的是SPI协议,并且只支持写,不支持读,因此控制OLED就是在SCLK的时钟下,通过SDIN进行命令和数据的传输。OLED的控制需要经过初始化、传数据和命令以及对显存设置等操作实现。

4.1 初始化

驱动IC的初始化代码,可以参考厂家推荐的设置,但需要根据开发板上OLED实际参数进行一些修改。

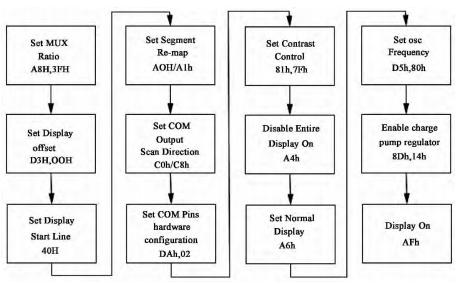

根据SSD1306数据手册的初始化说明,具体步骤如图4所示。初始化的实现就是对SSD1306进行写命令。

图4 SSD1306初始化步骤

评论