利用16位DAC实现20位分辨率的设计(图)

引言

随着dsp芯片处理数据能力的提高,数字信号处理系统的精度要求也越来越高。考虑到系统要求的是相对精度,而非绝对精度。为了获得最佳相对精度,本文提出一种创新的解决方案,即在精密dac后端使用可编程增益放大器(pga)。

系统框架结构

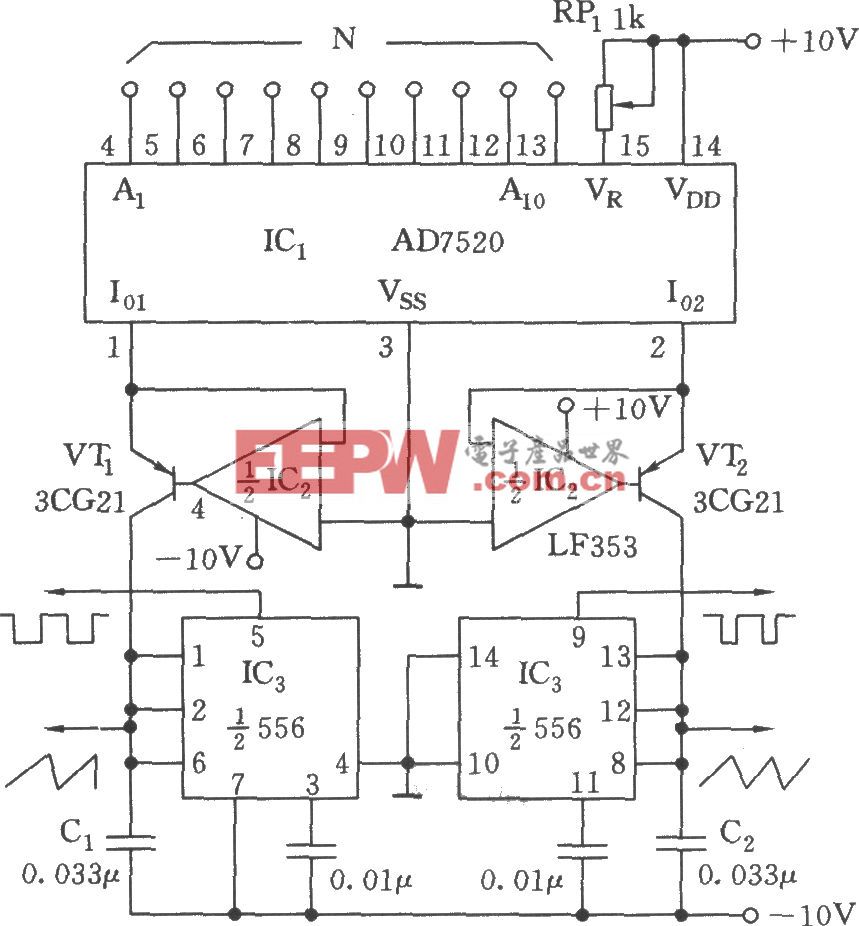

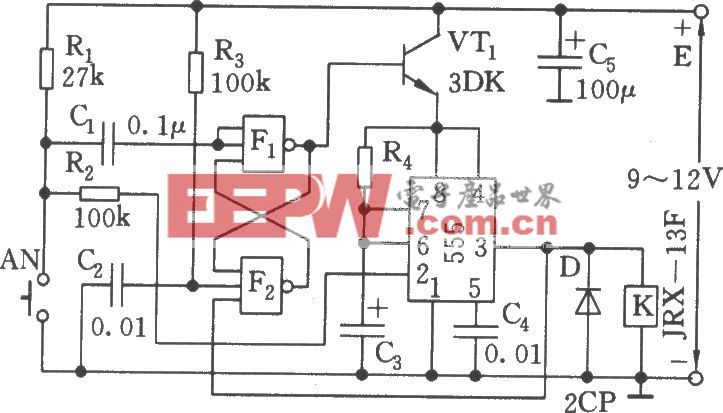

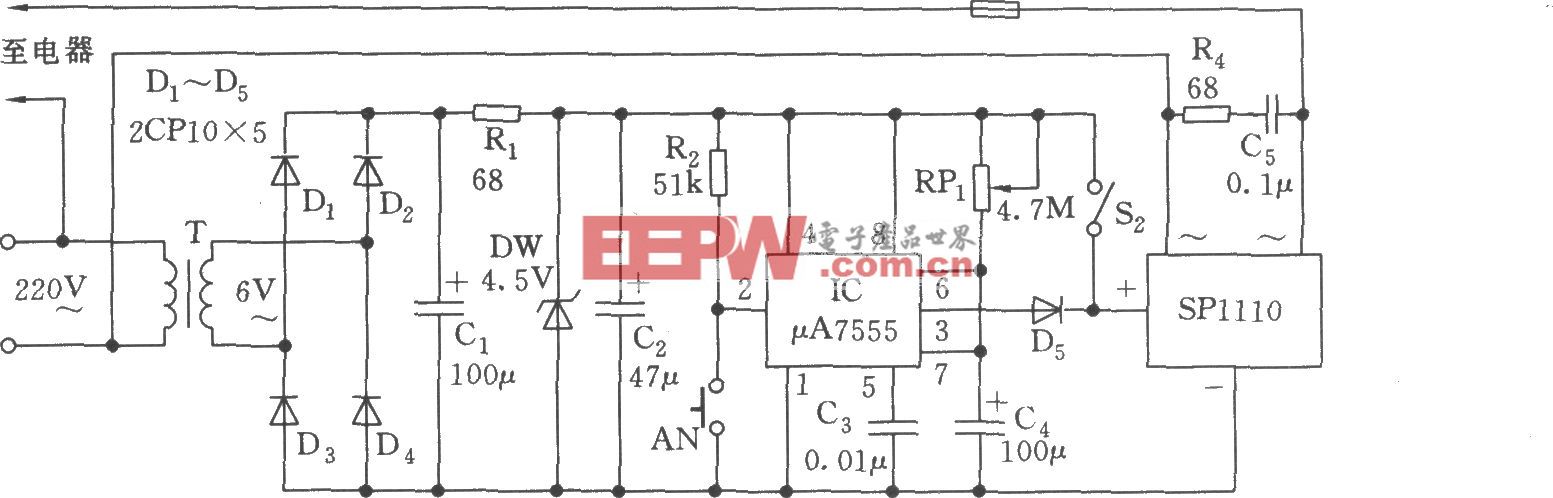

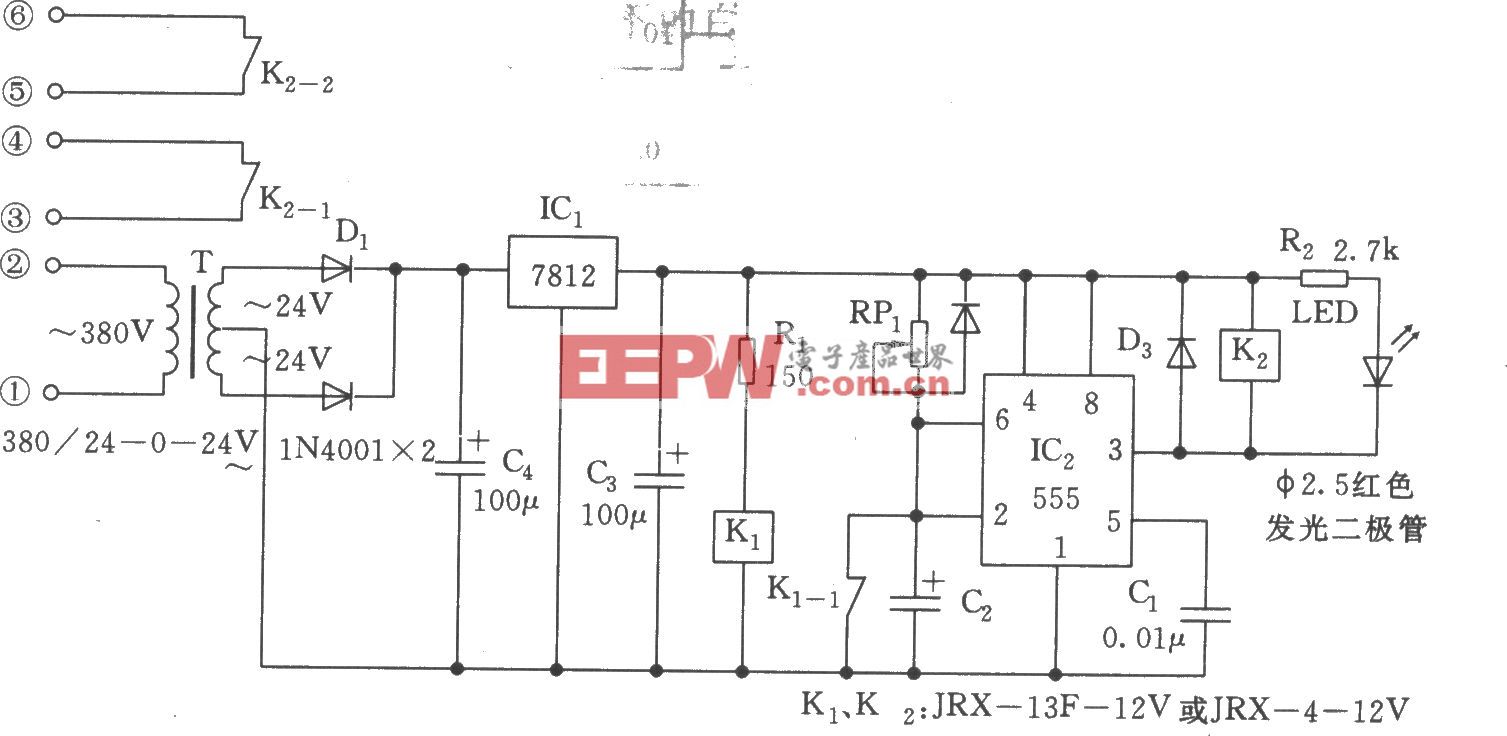

该系统主要包括以下几个部分:dsp、dac、dac后端低通滤波电路以及两个数字可编程运放pga205,如图1所示。系统中dsp采用了ti公司的tms320vc5402,它有一组程序总线和三组数据总线,高度并行性的算术逻辑单元alu、专用硬件逻辑片内存储器、增强型hpi口和高达100mhz的cpu频率,可以在一个周期里完成两个读和一个写操作。

d/a采用了adi公司的一种16位、低功耗数模转换器ad7846,实现了高速同步数模转换。可编程增益放大器采用的是美国bb公司的具有低增益误差的pga205,它可采用4.5~18v的电源工作,通过与cmos与ttl兼容的输入端来设定增益,并能提供快速的稳定时间。

硬件实现

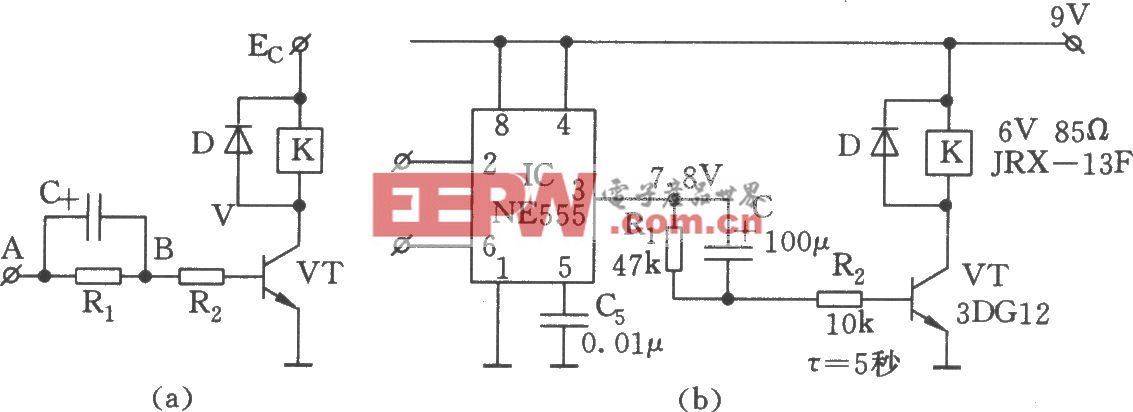

tms320vc5402和ad7846是通过vc5402的并行i/o接口来实现数据交换,通过地址线来对ad7846的四个数字逻辑进行控制的。

将cs和r/w均置为低电平时,开始向该dac写数,经过一段延时,将ldac置为高电平,clr置为低电平,dac进行数模转换。最后,将r/w和clr均置为低电平,即将该dac锁存器清零。当然,也可以通过cpld来对其进行控制。 图2是dsp和ad7846接口电路,图中省略了控制信号的电平转换电路部分以及dac的参考电压供电电路(ad7846由ad1580提供1.25v的单极性参考电压,ad7846最终输出单极性峰峰值为1.25v的正弦波)。dac后端低通滤波采用10阶1khz巴特沃斯低通滤波电路,有很好的幅频特性。 ad7846在16bit分辨率条件下为

评论