基于AD9650的高速数据采集系统的设计方案

本文引用地址:https://www.eepw.com.cn/article/227096.htm

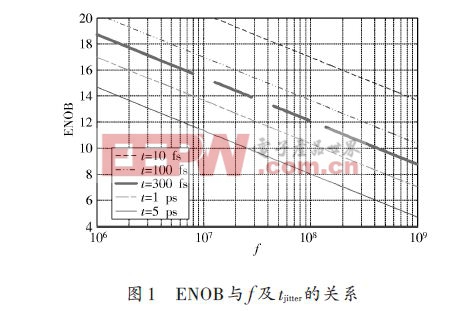

本文引用地址:https://www.eepw.com.cn/article/227096.htm忽略其他因素,仅考虑时钟抖动对ADC性能的影响,由式(1)可知,若要对20 MHz的中频信号进行采样,同时保证74 dB以上的SNR,则要求时钟抖动最大为1.588 ps RMS.且ADC电路的时钟抖动(tjitter)与采样时钟抖动(tjitter_clk)和ADC器件自身孔径抖动(tjitter_adc)之间存在如下关系:

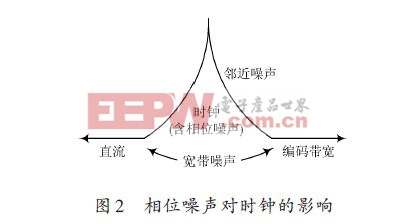

另外,采样时钟的相位噪声对ADC 性能有着重要影响。若采样过程用单位圆来表示,则每通过一次零相位,ADC 进行一次采样。采样时钟上的噪声将对相应矢量的顶点位置进行调制,从而改变发生过零的位置,造成采样过程提前或编码过程延迟。而采样时钟上的噪声矢量可能是相位噪声所导致的。如图2所示。

图2 中,理想情况下时钟信号应为单谱线。然而,受电源噪声、时钟抖动等因素影响,频域中存在大量能量分布在理想频率附近,代表相位噪声的能量。由于相位噪声往往可能扩展至极高频率,所以,它会使ADC的性能下降[6].采样过程实质是一个采样时钟与模拟输入信号的频域卷积过程,这个卷积过程在整个频谱域有效,同时在微观上也同样有效。因而,图2所示的时钟频率周围集中的相位噪声也将与模拟输入进行卷积,造成输出的数字信号频谱失真。

采样时钟相位噪声通常以单边带相位噪声来衡量,即:

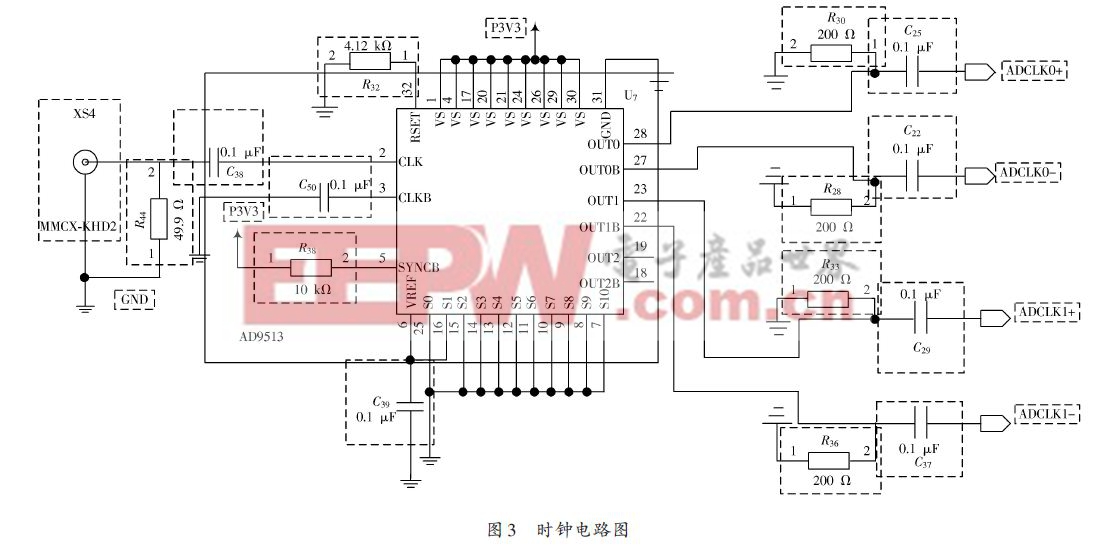

由此可以计算出采样时钟相位噪声,作为系统设计的依据。在本系统中,为保证时钟特性,时钟源由高精度晶振提供,时钟抖动控制在1.2 ps RMS以内,相位基底噪声为-165 dBc/Hz.板上时钟转换选用AD 公司的AD9513,其附加的时钟抖动为300 fs,输出的时钟信号性能满足要求。它实现对单路时钟转两路LVDS信号,给AD9650 提供采样时钟,同时给FPGA 提供同步控制时钟。图3给出了时钟电路设计原理图。

2.3 前端电路设计

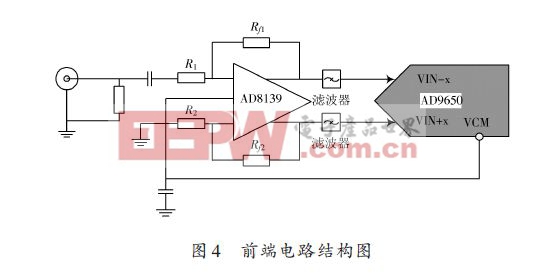

ADC前端电路主要完成对模拟输入幅度、信号形式的调整。它采用交流耦合方式,通过差分放大器,实现对信号幅度调整,同时实现单端输入信号转差分信号。并且,通过后续的滤波器实现信号的滤波。其结构如图4所示。

虽然差分运放是有源器件,使用中会消耗功率,且产生噪声,但它的性能限制比变压器少,可以在必须保留直流电平时应用,而且放大器增益设置简单灵活,且通带范围内提供平坦的响应,而没有由于变压器寄生交互作用引起的纹波。

ADC的 S (N + D) (信号噪声失真比)是决定驱动放大器的关键因素。如果在目标频率范围内,驱动放大器的THD ( 总谐波失真加性噪声) 总是优于ADC 的S (N + D) 值 6~10 dB,那 么 所 有 由 放 大 器 造 成 的S (N + D)降低将相应限制在接近0.5~1 dB.

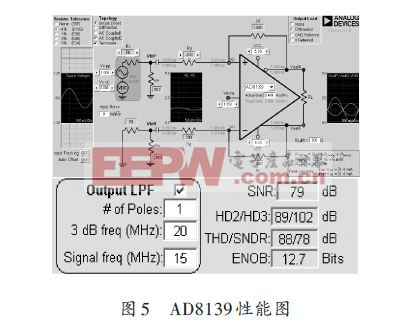

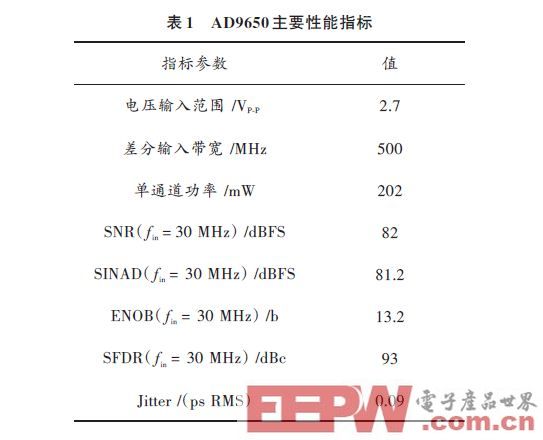

利用ADI 公司提供的ADI DiffAmp Calculator 软件可得到前端电路仿真图,如图5所示。由文献[3]可知在输入信号为15 MHz时,AD9650的 S (N + D) 为82 dB,而图5 中AD8139 的THD 为88 dB,满足上述要求。综合考虑增益及通带内响应及输入阻抗等因素,前端电路采用ADI公司的差分运放AD8139.

3 方案设计系统结构及实物

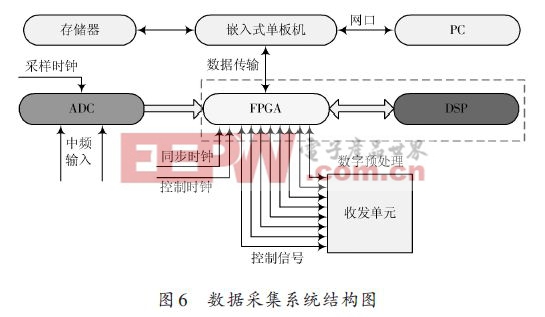

根据系统要求,设计的高速大动态范围ADC 数据采集系统,结构如图6所示,主要包括模数转换模块、数字信号预处理模块、数据传输模块和嵌入式单板机等。

评论