基于AD9650的高速数据采集系统的设计方案

随着数字信号处理技术的发展,越来越多的信号处理环节可以通过后端的软件处理完成,但这反而使得电子设备对前端数据采集系统的要求不断提高。因为后端软件的处理效果归根结底依赖于数据中所包含的信息量,只有提高数据采集的动态性能,才能保障后端处理的效果。长期以来,在数据采集领域,高速大动态范围ADC系统的设计与实现始终是研究的热点。当雷达工作在高杂波的电磁环境中,探测对象的RCS或多普勒信息非常微弱时,就对设计实现高速大动态范围数据采集系统提出了迫切的需求。

本文引用地址:https://www.eepw.com.cn/article/227096.htm目前,国内对高速大动态范围ADC数据采集系统设计主要依赖于芯片的指标而缺乏系统的研究和总结。本设计旨在通过优化系统设计,结合动态性能优越的模数转换芯片,实现一个高速大动态范围数据采集系统。

1 系统性能指标要求

本系统需完成的主要功能为:雷达同步控制;中频数据采集,数字正交解调;信号预处理。同时为了降低便携设备的功耗,预处理器拟采用低功耗处理器。由于要求动态范围大,中频采集需采用高精度的数据采集芯片,设计为2个通道,要求单通道量化位数不小于14 b,有效位数不小于12 b,输入信号范围2 Vp-p,且满足低功耗要求。

2 关键技术

如何保证大动态范围是设计中的关键点,同时也是难点所在,设计中从如下几方面进行考虑。

2.1 ADC芯片的选型

为了获得高速度、大动态范围,数据采集系统对ADC 的速度和量化精度的要求越来越高,而ADC 的速度和量化精度与其结构紧密相关。

目前常用的高速ADC类型主要有快闪型和流水线型。快闪型ADC 由于采用了全并行结构,具有超高速、宽输入带宽的优点,但其硬件规模随分辨率的增加呈指数增长,分辨率一般为4~8位,且存在高功耗、高成本、“闪烁码”等问题,将它应用于数据采集系统将会造成分辨率低、成本高、能耗大等弊端。而流水线型ADC具有较高的分辨率,量化位数一般为12~16位,较高的采样速率,一般为1~250 MSPS.流水线型ADC 将ADC与DAC结合,采用多级流水结构,解决了快闪式ADC无法达到较高分辨率的缺点,同时兼顾了快闪式ADC 的转换速度。因此,本文选择流水线型结构的ADC 芯片来实现高速大动态范围数据采集系统设计。

本文选择了AD公司的AD9650系列芯片。AD9650是一款双通道、16位流水线结构模数转换器,为解决高频(最大300 MHz)、大动态范围信号的数字化而设计。

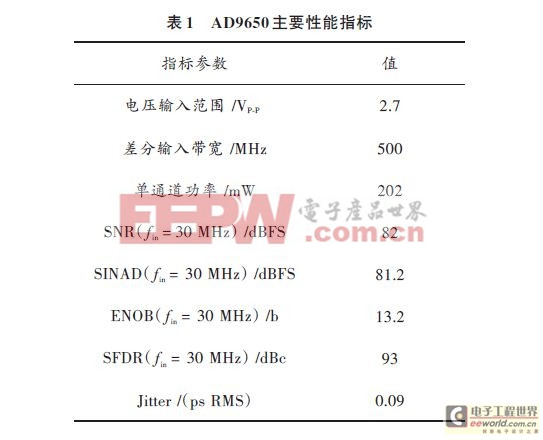

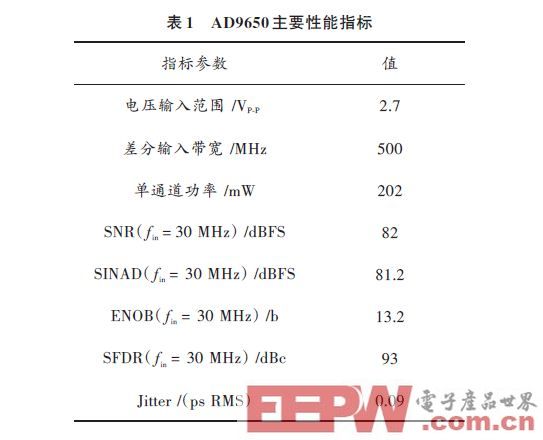

它具有集成ADC 采样保持输入、可选择片上Dither 模式、集成输入时钟1~8 分频等诸多特点。AD9650 输出信号模式可选择,默认输出为1.8 V CMOS,通过3线SPI接口,可配置工作模式,实现输出1.8 V电平的LVDS数字信号。它具有灵活的掉电选项、采用1.8 V单电压供电,提供了重要的节能特性。片上Dither选项能够提高低电平模拟输入的无杂散动态范围(Spurious Free Dy-namic Range,SFDR)。AD9650的主要性能指标见表1.

2.2 系统采样时钟性能

ADC 芯片受时钟控制进行采样,时钟质量对采样精度影响大,制约着系统所能达到的有效位。系统时钟主要性能指标包括时钟抖动和相位噪声。下面分别讨论两个指标对采样系统的影响。

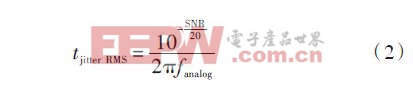

时钟抖动表征了模拟输入实际采样时采样时间的不确定性。由于抖动会降低宽带ADC 的噪声性能,因此,ADC噪声性能的下降将反映出时钟抖动情况。与系统信噪比(Signal-to-Noise Rate,SNR)边界值(单位:

dB)之间存在的关系如式(1)所示:

式中:fanalog表示模拟输入频率;tjitter表示时钟抖动,整理公式(1)得:

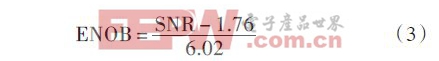

ADC有效位数(Effect Number of Bit,ENOB)与SNR的关系:

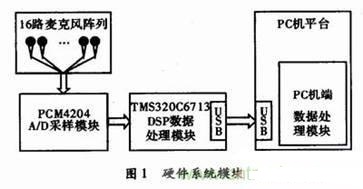

由式(1)和式(3)可得系统有效位数与模拟输入频率及系统时钟抖动的关系图,如图1所示。

评论