复杂可编程逻辑器件在通信数据传输中的应用

3.4 LAN 控制信号产生

lan91c93是一款嵌入式以太网控制器,和OMAP一起构成了嵌入式的以太网网络接口卡。OMAP用异步的FLASH接口时序来访问lan91c93,由于lan91c93没有片选输入端,所以把flash的片选和读写信号通过作一定处理后输出给lan91c93。OMAP把CS1空间分配给了lan91c93,当nFLASH_CS1为低时,把nFLASH_WE,nFLASH_OE输出给nLAN_WE,nLAN_OE,否则nLAN_WE,nLAN_OE为高电平。同时把LAN_RDY信号通过CPLD透传给OMAP,通知OMAP lan91c93准备好数据的交换。

4 仿真和实测

4.1 数据接收状态仿真

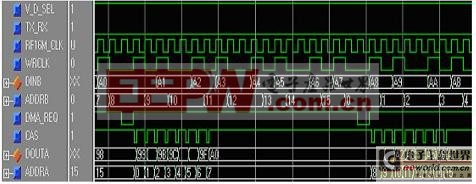

置V_D_SEL 为高,TX_RX 也为低,表示现在处于数据接收状态。依据时序关系产生所需的时钟,复位信号;产生AD9861 数据线上的数据,

图7 数据接收状态信号时序

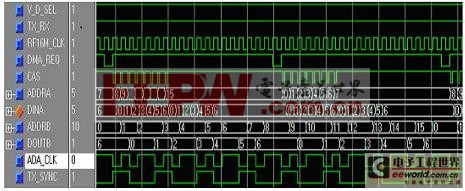

4.2 数据发射状态仿真

置V_D_SEL 为高,TX_RX 为高,表示现在处于数据发射状态。依据时序关系产生所需的时钟,复位信号;产生EMIFF 接口数据线上的数据,模拟OMAP 输出的发射数据; 模拟产生ADA 使能输入控制信号AD_DA_ENABLE;SDRAM CAS 信号等等。如下图所示,ADA_CLK为内部产生的6.4M时钟,输出作为ad9861的DA转换的主时钟。对ADA_CLK的上升沿计数得到AD9861侧的地址ADDRB,当ADDRB为8或0时,产生一DMA中断,触发OMAP通过EMIFF接口把发射数据输出到EMIFF接口数据总线上,每个DMA请求写8个数据,产生8个低脉冲的CAS信号,对CAS的脉冲个数进行计数,得到OMAP侧地址的低3位,最高位由ADDRB的MSB取反得到,这样能避免读写冲突。DINA为EMIFF接口数据线上的数据,用CAS延迟信号的下降沿来锁存DINA,满足EMIFF的SDRAM写时序,可以正确地把数据写入到双口RAM中。DOUTB为输出给DA的数据,同时按照时序要求产生一发射同步信号TX_SYNC,用来指示发射的I和Q,用ADA_CLK的上升沿采样,正好能采样到DOUTB和TX_SYNC的中间,确保数据的稳定性。

图8 数据发射状态信号时序

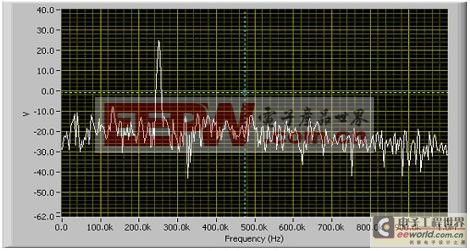

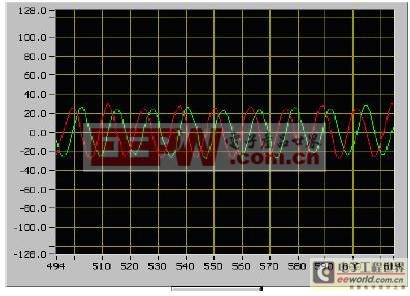

4.3 数据实测结果

记录的频谱图,时域波形图和星座图如下,频谱为250K,跟信号源设置的频偏一致。时域波形I 落后Q 90 度,且I 的最大值对应于Q 的零点,两者的正交性得到了保证,星座图是一个圆同样证明了这一点。

图9 接收信号频谱图

图10 接收信号时域波形图

图11 接收信号星座图

评论