复杂可编程逻辑器件在通信数据传输中的应用

3.2 时钟产生

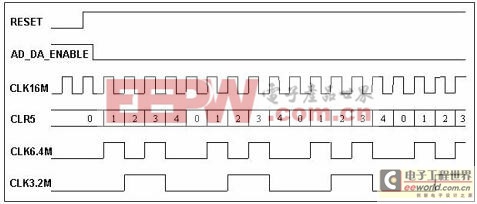

CPLD输入时钟有来自射频的16M时钟,来自外部晶振的32.768M时钟和来自OMAP接口的75M时钟CLK。其中16M时钟用于产生数据应用时AD9861所需要的3.2M、6.4M转换时钟,32.768M时钟用于产生语音应用时AD9861所需要的1.6384M、3.2768M时钟以及CODEC AIC1110所需要的8K和2.048M时钟。SDCLK本可以作为OMAP读写的主时钟,但必须要使用CAS信号作为读写允许配合使用才行,为了节省布线资源,不用读写允许,就直接用CAS作为写时钟及OMAP侧的地址产生使用,而SDCLK则用于产生一些同步脉冲。这些产生的时钟除了输出给外部芯片外,还在CPLD内部作为地址产生的时钟使用。3.2M和6.4M的时钟产生是把16M的时钟从0到4计数,由reset和ad_da_enable给计数器清零,这样的模5计数器的最低位即为6.4M,次低位为3.2M时钟。这种时钟产生的方式只需要三个DFF,节省逻辑资源,而且不会产生毛刺,但产生的时钟占空比不是50%,实践证明在低速应用时,AD9861是可以正常工作的。系统的时钟时序如图3所示。

图3 时钟时序

1.6384M和3.2768M时钟的方法同理,只是需要把32.768M的时钟20分频而已,同样计数器的清零由reset和ad_da_enable控制,这样得到的模20计数器的第2位即为3.2768M,第三位为1.6384时钟,时序跟上图相似,这里就不再给出。

这四个时钟被分时赋给AD9861的主时钟ADA_CLK,具体是哪个时钟被赋ADA_CLK,由收发切换信号TX_RX,语音和数据选择信号V_D_SEL控制。当TX_RX=’0’ 且V_D_SEL=’0’时,输出给ADA_CLK的时钟为1.6384M;当TX_RX=’1’且V_D_SEL=’0’时,输出给ADA_CLK的时钟为3.2768M;当TX_RX=’0’ 且D_SEL=’1’时,输出给ADA_CLK的时钟为3.2M;当TX_RX=’1’ 且V_D_SEL=’1’时,输出给ADA_CLK的时钟为6.4M。

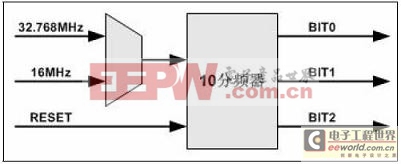

为了进一步节省资源,可以考虑把模5和模20的计数器共用,方案如图4所示,BIT1和BIT2即为所需的时钟,这时前端时钟源由V_D_SEL选择,BIT1和BIT2的选择输出由TX_RX控制。

图4 模5 模20 计数器共用的时钟产生方案

2.048M的时钟产生由32.768M时钟16分频得到,计数器的复位由reset和语音允许audcken控制,这样得到的模16的计数器的高位即为2.048M时钟。8K时钟是对产生的2.048M时钟256分频得到。

3.3 地址产生

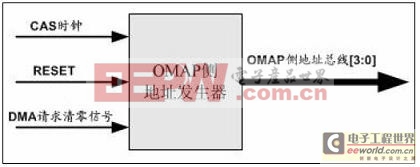

在使用双口RAM作为数据缓存时,有两部分地址产生电路:OMAP侧地址产生电路和AD9861侧地址产生电路。AD9861侧地址产生电路和OMAP侧地址产生电路大致相同,但由于这2个地址发生器同时使用,所以不能复用。OMAP的地址发生器框图如下:

图5 OMAP 的地址发生器

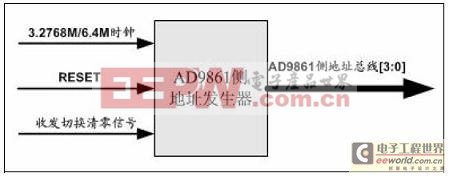

CAS 时钟只负责对低3 位地址进行计数,而最高位由于选择2 个8×8RAM 中的一个,为防止adda 和OMAP 同时读写同一个RAM,将OMAP 侧的高位地址线取值为AD9861 侧的地址最高位的反相。DMA 请求清零信号作用:在AD9861 侧每触发一次DMA 请求,就生成一个DMA 请求清零信号,用于复位OMAP 侧地址发生器,避免由于某此误触发引起OMAP 读写地址混乱。AD9861 侧地址发生器如下:

图6 AD9861 侧地址发生器

4位地址总线的低3位用于选择同一片RAM中的8个地址,最高位用于选择2个8×8RAM中的一个,收发切换信号用于在收发切换时给地址发生器清零,复位由于逻辑误触发导致的地址总线错误。

评论