基于FPGA的宽带数字接收机变带宽数字下变频器

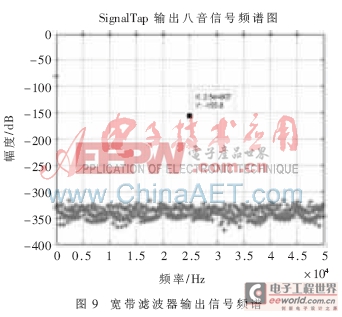

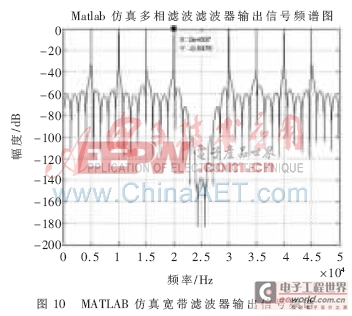

将采样率100 MHz、带宽40 MHz的八音信号输入VB-DDC系统。VB-DDC配置成宽带多相滤波器滤波,将硬件调试输出I_out_F、Q_out_F导入MATLAB进行频域分析如图9所示,其与图10的MATLAB理论仿真结果对比,可得设计满足要求。

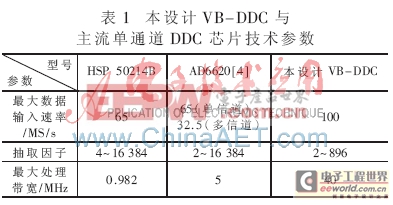

本文基于FPGA芯片Stratix II EP2S60F672C4设计了一个适用于宽带数字接收机的VB-DDC。该VB-DDC可根据处理信号带宽要求,灵活选择下变频器结构为传统结构的窄带DDC或者基于多相滤波结构的宽带DDC,也可以联合使用两种结构。表1列出了本设计VB-DDC与Intersil公司、ADI公司的两种单通道DDC芯片产品的主要技术参数,其中HSP50214B为目前各种单通道DDC产品中功能最强的型号。本设计的VB-DDC在最大数据输入率和最大处理带宽这两项最重要的性能指标上占有很大优势。本设计的VB-DDC已经应用于宽带数字接收机系统。

参考文献

[1] Intersil.HSP50214B Data Sheet.2000,5.

[2] ANALOG DEVICES.AD6645 Data Sheet.2006.

[3] San Jose. Phase-locked loops reconfiguration(ALTPLL_RECONFIG) megafunction user guide. Altera Corporation,2008,7.

[4] ANALOG DEVICES. AD6620 Data Sheet.1998.

评论