基于CPLD的视频叠加

三、十字坐标的实现

采用CPLD,取同步分离芯片的复合同步信号输出,场同步信号输出。当复合同步信号的上升沿到来时,对系统时钟(24MHz)计数,当场同步信号上升沿到来时对复合同步脉冲计数,当系统时钟计数计等于24000000/15625/2=768且复合同步脉冲计数计到106~206时输出一个高脉冲(5V峰峰值)。再将该信号与原视频信号叠加,即可在显示屏正中显示一垂直线,如下图:

当复合同步信号的上升沿到来时,对系统时钟(24MHz)计数,当场同步信号上升沿到来时对复合同步脉冲计数,当系统时钟计数计到558~938且复合同步脉冲计数等于156时输出一个高脉冲(5V峰峰值)。再将该信号与原视频信号叠加,即可在显示屏正中显示一水平线,如下图:

再将两路输出信号或逻辑,即可得到十字坐标的显示。

本文介绍了电视机行场扫描的原理,提出了一种视频信号叠加的思路,采用CPLD作为控制器,方便灵活,只需根据一定的算法还可实现任意图形和汉字字符的叠加,由于时间有限,本文不再叙述。

附录:

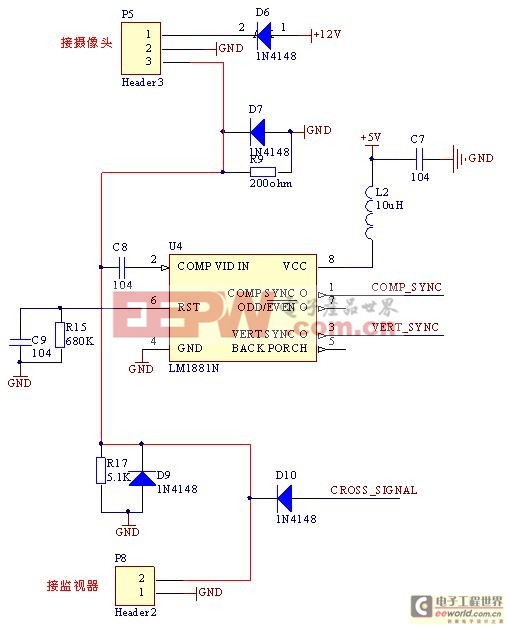

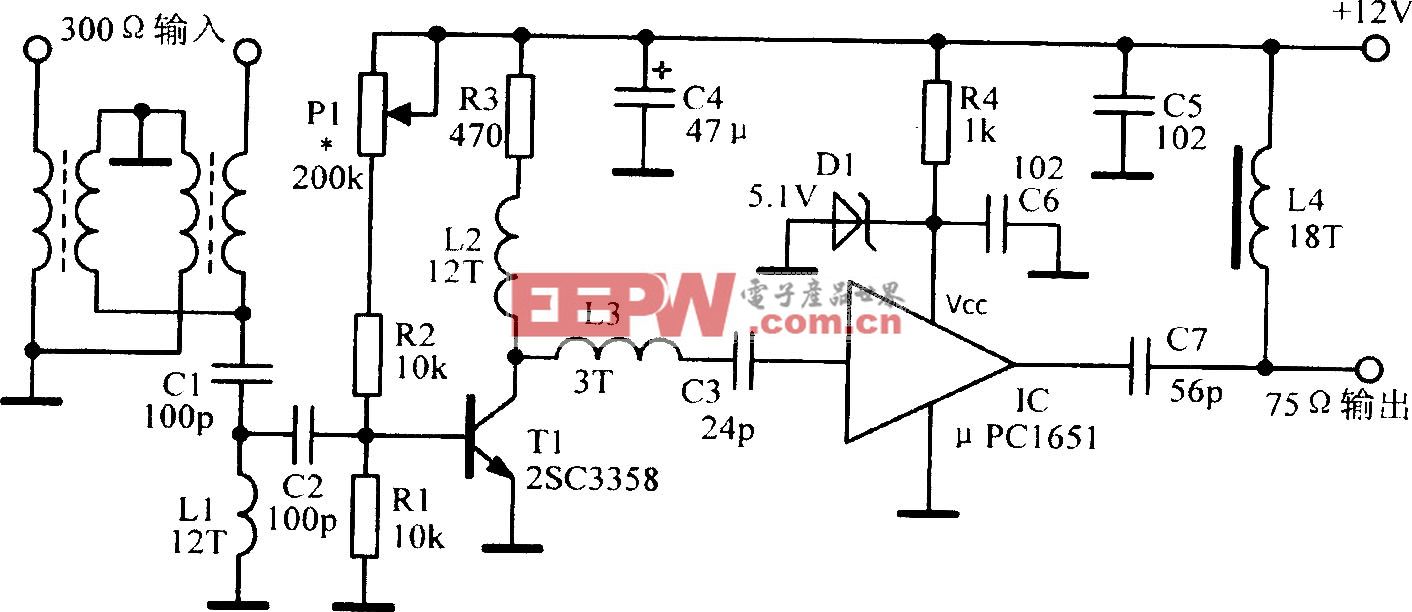

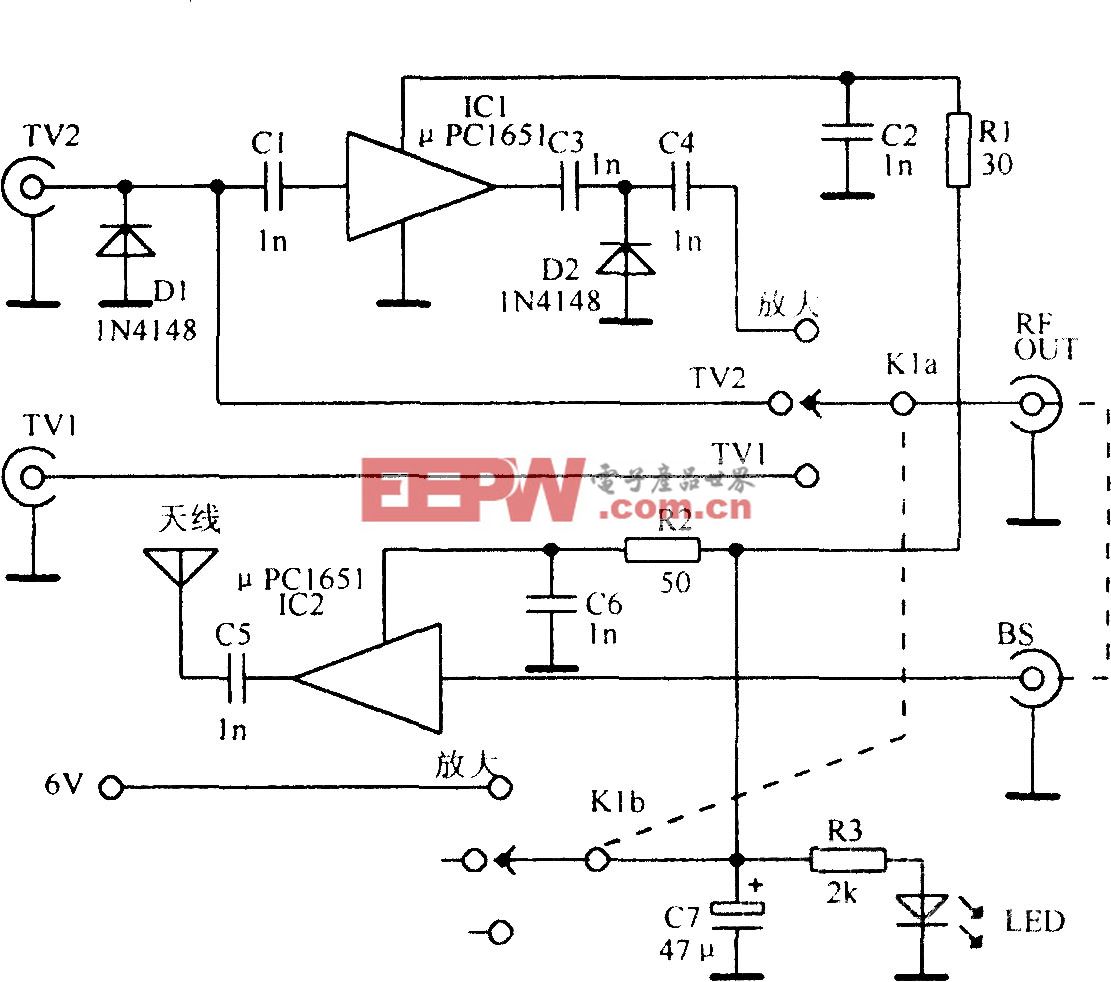

1、 原理图

评论