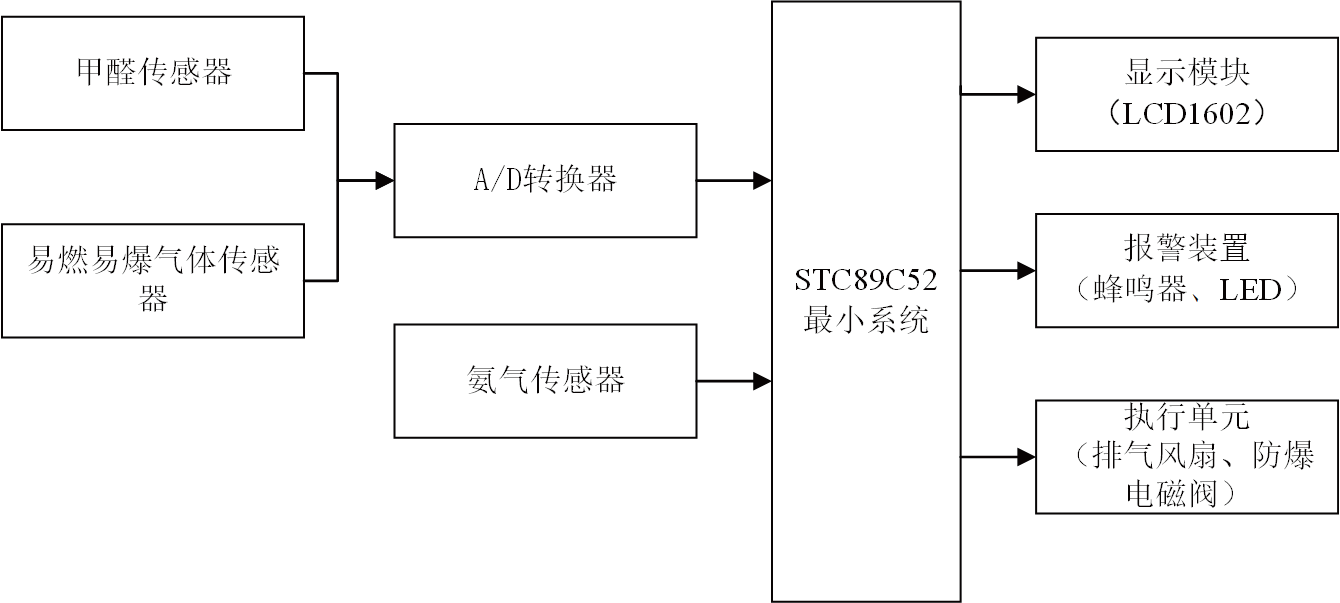

51单片机+CPLD让系统更高效

三、单片机与CPLD接口设计

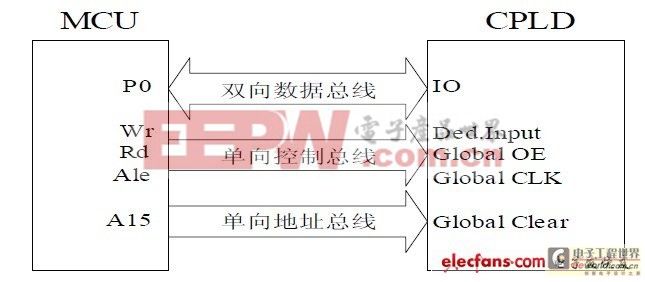

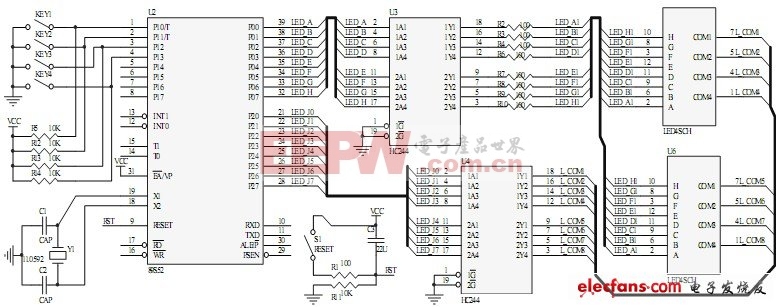

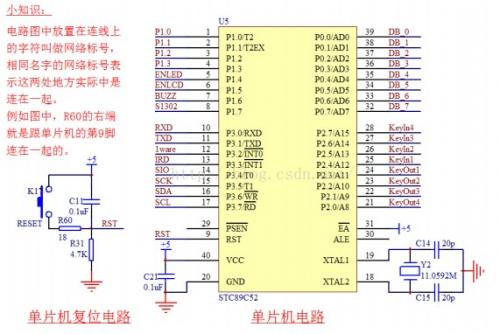

以上经典电路中,系统扩展使用了单片机总线模式,各个对象采用的三总线连接,根据这种电路结构,这里给出一种单片机同CPLD 的总线接口模式,如图4 所示。

图4 单片机与CPLD总线接口示意图

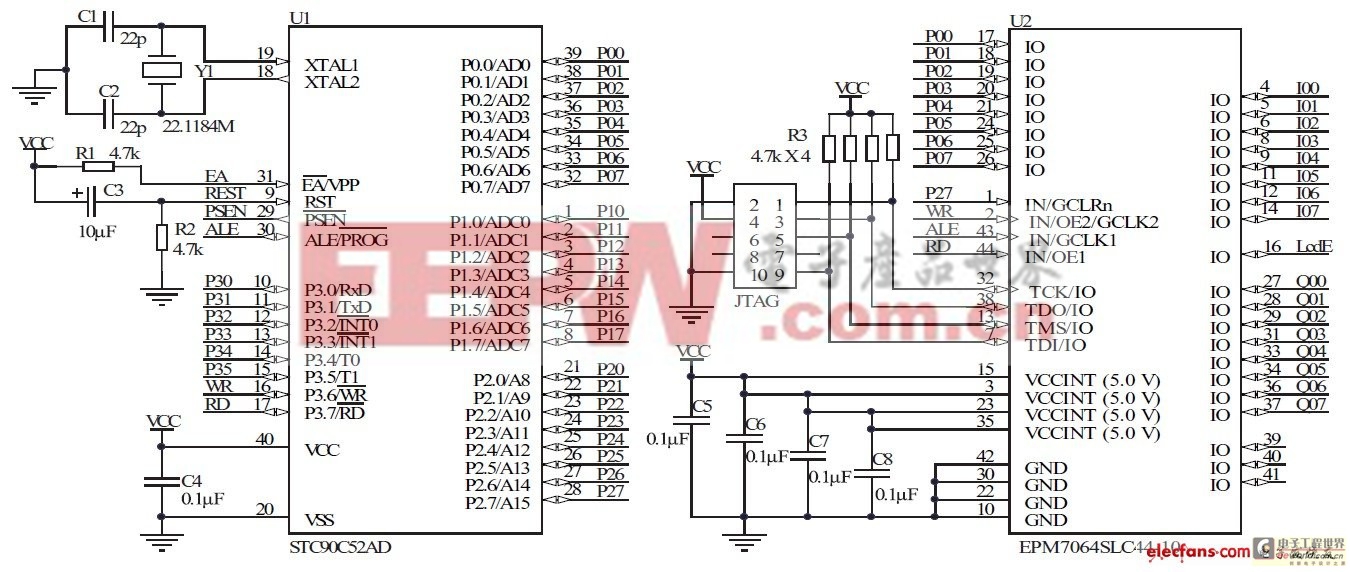

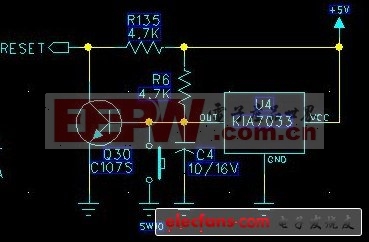

这里选择A l t e r a 公司早期的EPM7064SLC44-10 为例,这是很老的一款CPLD器件,是5V 供电。其实选择什么CPLD 型号并不是关键,关键是学习用CPLD 代替分立器件的思想和方法。数据总线P0 口同CPLD 一般IO 口相连,完成数据和低8 位地址传送;控制总线包括单片机读写控制信号Rd(P3.7) 和Wr(P3.6),以及地址锁存信号ALE(Address Lock Enable)和高位地址线A15(P2.7) 通过CPLD 的全局信号引脚输入,包括全局时钟输入:INPUT/GCLK1, 全局清零输入INPUT/GCLRn, 全局使能输入INPUT/OE1,INPUT/OE2, 这几个信号有专用连线与CPLD 中每个宏单元相连,保证信号到每个宏单元的延时相同并且延时最短。实际电路原理图如图5所示。

图5 MCU与CPLD接口电路原理图

这样一块CPLD 器件就代替以上除单片机外的7 块芯片了,在电路板上将节约大片的PCB 面积,好处还远不止这些,因为CPLD 是二次开发的,其内部电路可以根据需要再次设计,反复修改,极大的增加了电路设计的灵活性。

读者看到这里,肯定对自己动手设计CPLD 电路充满了期待,下面介绍如何借助工具软件开发CPLD 内部电路。

四、CPLD开发介绍

一般来说,CPLD 生产商都有配套的开发工具, 这里介绍ALTERA 公司的一款易学易用的CPLD 开发软件MaxPlusII,虽然该公司最新版的软件是QuartusII,但针对某些具体的器件,选择MaxPlusII 还是很方便的。该软件入门教程请到百度搜索《MaxplusII 设计CPLD 入门》,很多手把手的资料。

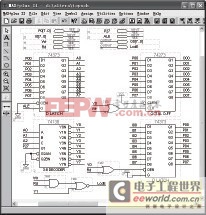

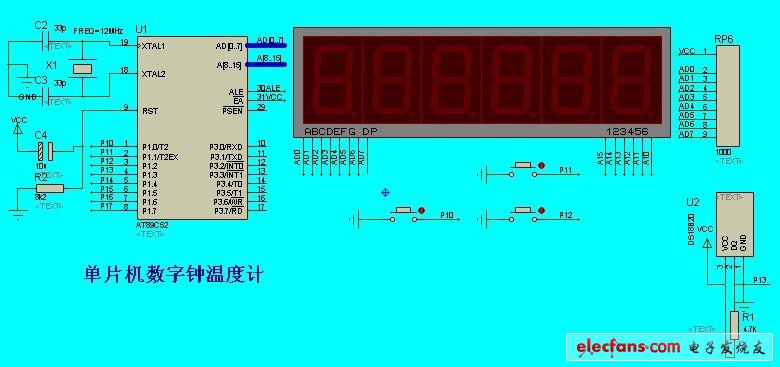

最容易的电路设计方法不外乎是直接绘制电路原理图。采用原理图输入,初学者甚至不需要额外学习就可以从事CPLD 设计。我们只需要在软件平台上从集成器件库调出对应的器件,绘制相同的电路原理图即可,实现以上功能电路原理图绘制完成后如图6 所示。

图6 原理图输入设计CPLD

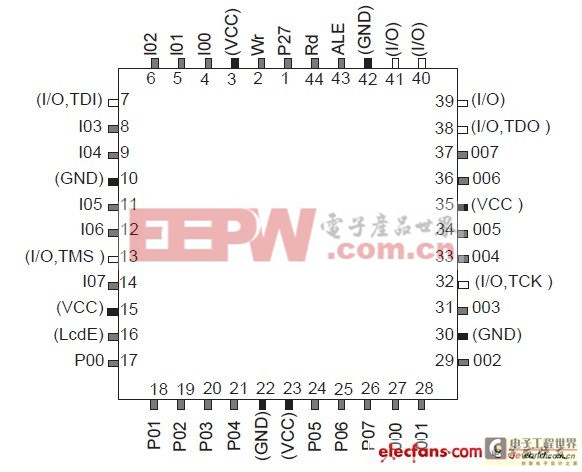

该原理图编译成功后,我们还需要根据实际电路连接图分配绑定引脚,引脚绑定如图7 所示,再编译就可以得到可供下载的文件*.pof 了,最后只需要将下载电缆连接到电路板上,仍然通过该软件即可完成下载。

正因为CPLD 的IO 脚是可以随意分配的,通常我们会结合实际的PCB 板设计布线的便利来调整引脚分配,引脚分配更改后,只需要重新分配引脚再编译下载即可。

图7 CPLD引脚绑定

除了原理图输入外,复杂的CPLD 器件开发,一般用硬件描述语言设计,常用的硬件描述语言有VHDL,VerilogHDL,这些硬件描述语言的掌握是需要系统学习的,基于硬件描述语言的片上系统设计,FPGA 开发目前已经成为高薪职业,社会需求巨大。用硬件描述语言开发CPLD 的方法与前面的原理图输入法类似,也需要编译纠错,时序仿真,引脚绑定,最后编译下载即可。

给CPLD 下载完程序,这块芯片就是你所设计的逻辑时序电路了,通常比分离元器件功耗更低,性能更优。

真正是基于上述思想, 笔者将51 单片机同CPLD 相结合,开发了一款适合初学者使用的学习板--Mini51 板。

评论