SemiDynamics详细介绍了一体化 RISC-V NPU

西班牙的 SemiDynamics 开发了一种完全可编程的神经处理单元 (NPU) IP,它结合了 CPU、向量和张量处理,可为大型语言模型和 AI 推荐系统提供高达 256 TOPS 的吞吐量。

Cervell NPU 基于 RISC-V 开放指令集架构,可从 8 个内核扩展到 64 个内核。这使设计人员能够根据应用的要求调整性能,从紧凑型边缘部署中 1GHz 的 8 TOPS INT8 到数据中心芯片中高端 AI 推理中的 256 TOPS INT4。

这是继 12 月推出的一体化架构之后发布的,本白皮书中对此进行了详细介绍。

“Cervell 专为 AI 计算的新时代而设计,在这个时代,现成的解决方案是不够的。作为 NPU,它提供从边缘推理到大型语言模型的所有功能所需的可扩展性能。但真正让它与众不同的是它的构建方式:完全可编程,由于开放式 RISC-V ISA 没有锁定,并且可以深度定制到指令级别。结合我们的 Gazillion Misses 内存子系统,Cervell 消除了传统的数据瓶颈,并为芯片设计人员提供了强大的基础,以构建差异化的高性能 AI 解决方案,“Semidynamics 首席执行官 Roger Espasa 说。

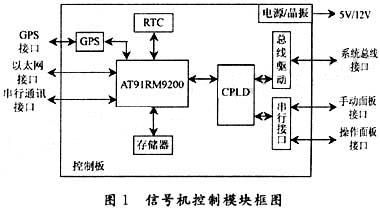

Cervell NPU 专为加速矩阵密集型作而设计,可实现更高的吞吐量、更低的功耗和实时响应。通过将 NPU 功能与标准 CPU 和矢量处理集成到统一架构中,设计人员可以消除延迟并最大限度地提高各种 AI 任务(从推荐系统到深度学习管道)的性能。

Cervell 内核与 Gazillion Misses 内存管理子系统紧密集成。这支持多达 128 个同步内存请求,消除了超过 60 字节/周期的持续数据流的延迟停顿。此外,还可以大规模并行访问片外内存,这对于大型模型推理和稀疏数据处理至关重要。

这可以保持完整的管道饱和,即使在推荐系统和深度学习等带宽密集型应用程序中也是如此。

该内核是完全可定制的,能够添加标量或矢量指令,配置暂存器存储器和自定义 I/O FIFO,并定义存储器接口和同步方案,以提供面向未来的差异化 AI 硬件。

这种 RTL 级别的深度定制,包括插入客户定义的指令,使公司能够将唯一的 IP 直接集成到解决方案中,保护其 ASIC 投资免受模仿,并确保设计针对功耗、性能和面积进行全面优化。开发模型包括早期 FPGA drop 和并行验证,以减少开发时间和风险。

Configuration | INT8 @ 1GHz | INT4 @ 1GHz | INT8 @ 2GHz | INT4 @ 2GHz |

C8 | 8 TOPS | 16 TOPS | 16 TOPS | 32 TOPS |

C16 | 16 TOPS | 32 TOPS | 32 TOPS | 64 TOPS |

C32 | 32 TOPS | 64 TOPS | 64 TOPS | 128 TOPS |

C64 | 64 TOPS | 128 TOPS | 128 TOPS | 256 TOPS |

评论