相位式光纤测量电路系统的设计与实现

2.2.2 频率信号产生电路的实现

频率信号产生电路在FPGA中频率控制模块的控制下,产生高精度正弦主振信号和本振信号,分别用于光调制和混频。此电路产生的信号要求频率可调,且具有高的频率稳定性和低的相位噪声,相位抖动小,以保证最终的测量精度。

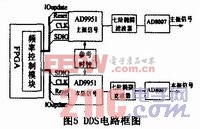

在本系统中,我们基于直接数字频率合成(DDS)技术进行信号产生。DDS的实现,使用芯片AD9951。AD9951是一个可控的频率合成芯片,具有32位频率转换字,最大合成频率为160MHz。系统中采用两块AD9951,分别产生主振信号和本振信号。FPGA通过该芯片的控制端口,对

其产生的信号频率进行控制。其控制时序如图4所示。

AD9951产生的频率信号具有一定的杂散,系统中使用七阶椭圆低通滤波器进行滤波,然后使用运算放大器AD8007进行信号放大。电路框图如图5所示。该电路产生的50MHz的正弦信号如图6所示。

2.2.3 混频鉴相电路

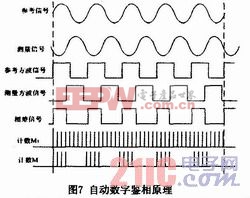

由于测量信号频率较高,直接对其进行鉴相难以达到良好的鉴相精度,因而在系统中采用混频的方法进行差频鉴相。在差频鉴相中,参考信号和测量信号同时与本振信号进行混频,滤除混频后高频分量,得到混频后低频参考信号和混频后低频测量信号。混频降低了信号频率,但保持相位差不变,便于鉴相操作。相位差的检测使用自动数字鉴相法。其原理如图7所示。参考信号和测量信号通过过零比较,得到参考方波信号和测量方波信号。比较两方波信号,得到两者之间的相位差信号,然后使用高频计数脉冲对相位差信号,然后使用高频计数脉冲对相位差信号进行计数。设参考信号和测量信号的周期为f,高频计数脉冲的频率为fc,一个周期内的计数值为M,则相位差为:△φ=2πMf /fc。为了减小偶然误差,提高鉴相精度,可以对多个周期计数求平均。设N个周期的计数值为M',则△φ=2πM'f/Nfc。

评论