PCIE 3.0 的接收机物理层测试方案

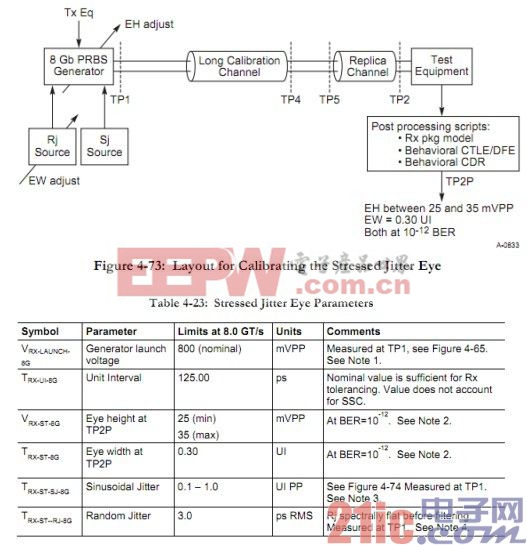

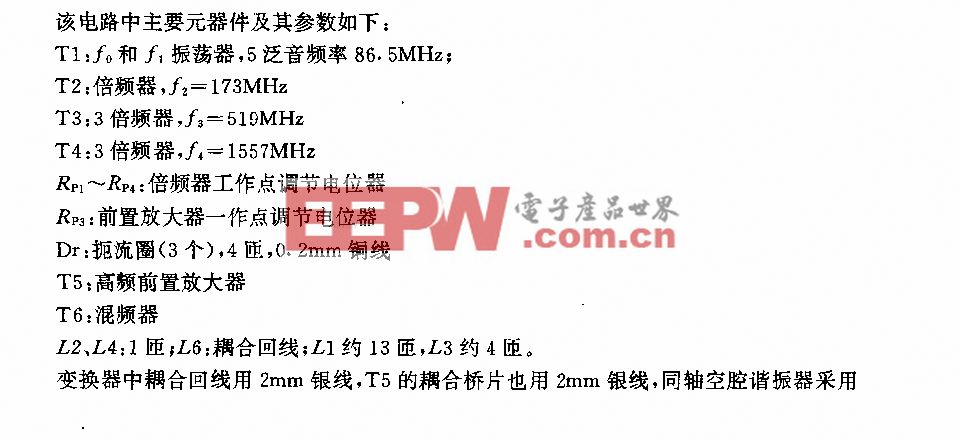

来自于PCIE 3.0 规范的接收机测试的抖动源校准连接图及要求:

示波器采集到数据后会自动导入到Sigtest 中进行测试分析,眼图测试的后处理(包括CTLE/DFE/CDR 等可以在Sigtest 中完成,也可以使用力科示波器SDA830Zi-A 中的

SDAII/EYEDOCTORII 软件完成),力科示波器中集成了Sigtest 软件。

PCIE 3.0 接收端抖动容限测试设置及连接示意图及测试结果:

接收机测试推荐使用的码型为Modified Compliance Pattern ;对于Add-In Card 被测件来说,误码测试仪输出的100MHz 的时钟需要连接到CBB 板的时钟输入端口;对于System 被测件来说,CLB 板上来自于被测系统的100MHz 时钟输出需要连接到误码仪的参考时钟输入,经过规范要求的PLL 滤波后,用于驱动仪器的信号传输。误码仪做误码检测时需要过滤到为了信号同步而插入的SKP 码。

评论