MAX1032结合CPLD的应用

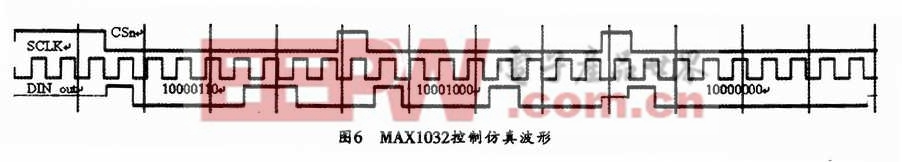

图6所示是Modelsim的仿真波形。SCLK上跳沿DIN_out的数据被MAX1032读取。本文引用地址:https://www.eepw.com.cn/article/191480.htm

程序的第二部分的作用是将MAX1032输出的串行采样结果存入CPLD内部的一个14位寄存器。采样结果DOUT_in_S是14位的串行序列。CPLD在SCLK的上跳沿读取数据后,可将其存到一个内部寄存器,再由DOUT选择输出寄存器的高或低八位数据读出。最后的采样结果是并行输出的。总共2个字节,末两位数据无效。对于外部时钟模式,可从加载转换启动字开始计算,在第16个SCLK下跳沿,芯片将输入采样结果。得到结果即可按照公式(采样电压=12x(转换成十进制的输出结果)/16384)进行计算。以下是这部分功能的可综合代码:

评论