捷联惯性组合导航系统的工程设计

3.1 FPGA软件设计

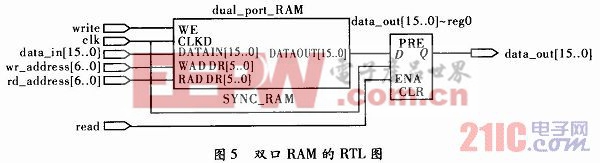

FPGA是按照主CPU的指令来执行对加速度计的数据采集和数据处理任务,然后将预处理的结果写入双端口RAM,供PC/104使用。FPGA内部的逻辑块包括时钟、A/D控制器、数字滤波器、双口RAM、接口单元等。数字滤波器的设计直接采用设计好的FIR滤波器的IP核。通过Verilog HDL语言对双口RAM的描述可以在FPGA内部实现双口RAM,并且进行读写控制。双口RAM在使用上需要注意的问题就是,可能会发生共享冲突,出现写入值和读出值出现混乱的状态。设计采用文献的方法设计双口RAM冲突解决方案。本文引用地址:https://www.eepw.com.cn/article/190720.htm

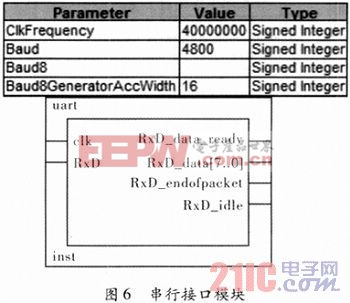

在FPGA内部实现一个串口模块,采用GPS接收机默认的4 800 bit·s-1,首先将系统的40 MHz时钟进行分频,一般对数据进行过采样,以便正确接收GPS接收机的数据。取过采样频率为波特率的8倍。有了4 800×8 Hz的频率之后,进行串并转换。为防止毛刺信号被误认为是起始信号,定义一个2位的计数器进行判断起始位4次。接着用状态机实现对起始位、数据和停止位的检测,就可进行数据的接收。通过Verilog HDL语言编写接收GPS数据程序,采用状态机方法检测GPS数据起始符,本系统采用$GPRMC,(UTC时间),A,(纬度信息),N,(经度信息),E,(速度信息),289.0,020710,10.3,W×5B协议,本系统只用位置和速度信息对捷联惯导系统进行校正。接收到的GPS数据为对应ASCII值的二进制数。

3.2 PC104软件设计

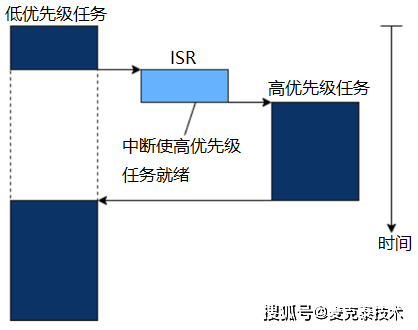

数据解算采用PC104为核心处理器。采集的陀螺和加速度计的信息经过误差补偿后,将陀螺仪测量的角速度数据进行解算,得到姿态矩阵,再用姿态矩阵将沿载体坐标系的加速度测量的比力信息转换到导航坐标系上,进行积分运算,同时根据姿态矩阵中的元素可以解算出姿态角信息。再用GPS测量得到的位置、速度信息和捷联惯导系统解算得到的位置、速度的差值作为观测量,通过卡尔曼滤波,修正导航系统的参数,为惯性元件提供误差修正,以提高导航精度。将得到的位置、速度、姿态等信息输出,进行控制载体。PC104对双口RAM的端口地址读/写操作的函数为inport(int protid)和outport(int portid,int value),protid为端口地址,value为要发送数据。

4 结束语

文中以PC104为核心处理器,辅以FPGA控制采集和A/D转换,形成双CPU协作模式,通过双口RAM进行通信,主CPU可以专心进行导航计算,避免了因数据采集工作而降低效率。双CPU并行工作,相互配合,大大地提高了系统的整体效率。系统体积小、精度高、结构简单、功耗小。将导航参数通过串口输出,可应用于船舶、车辆、飞机等,能满足导航和定位的要求。

评论