捷联惯性组合导航系统的工程设计

2.2 导航解算模块

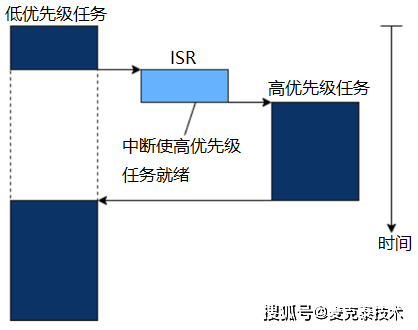

导航解算模块是捷联惯性组合导航系统的核心。该部分的功能主要完成姿态矩阵的即时修正、位置姿态信息的求取和卡尔曼滤波等运算。要求导航计算机对浮点数据的处理能力强,并且整个导航计算中涉及大量的矩阵计算,运算量较大。PC104采用中断机制工作,需要处理FPGA数据准备好中断请求、导航计算、滤波计算。

2.3 FPGA和PC104之间的通信

设计采用两个控制器结构,PC104要进行导航解算,就要将FPGA采集处理后的数据接收。若通过FIFO来传递数据,由于FIFO的先进先出原则,则存在一个采用频率和解算速率的配合问题。而系统又要求较好的实时性,即每次要进行解算都能立即得到最新的实时数据。双口RAM方式无论是通信速率还是硬件实现的难易程度上都是处理器问高速通信的最佳选择。系统采用双口RAM实现FPGA和PC104之间的数据共享。本文引用地址:https://www.eepw.com.cn/article/190720.htm

双口RAM存储器具有两套独立的读写控制线、地址线和数据线。可以自由访问,互不干扰。用FPGA实现双口RAM的功能可以较好地解决并行性和速度问题,而且其灵活的可配置特性使得基于FPGA的双口RAM易于进行修改、测试及系统升级,可降低设计成本,缩短开发周期,减小了导航计算机的体积。因此本设计直接采用FPGA构建双口RAM,同时进行读写操作控制。PC104总线上的I/O地址范围为0000H~FFFFH,选取地址段0200H~027FH作为双口RAM的地址段,共128个地址单元。FPGA与PC104引脚电平不同,FPGA的I/O口供电电压为3.3 V,PC104的总线为5 V TTL电平。因此,为使系统安全稳定地工作,需要一个电平转换器件。在PC104和FPGA之间使用起电平转换作用的CPLD,同时由它产生地址译码电路。

3 软件设计

软件设计以满足导航参数解算为主,采集模拟的惯性测量器件及GPS数据,通过双CPU之间的软硬件形成呼叫和应答机制。由FPGA负责加速度计和陀螺仪输出信息的采集及数据处理,采用FPGA接收读取GPS的数据;PC/104工控机负责对FPGA采集到的数据进行解算。对控制采样及数据处理模块的软件设计主要是控制A/D转换,构建内部存储器、数字滤波器和串行接口等,采用硬件描述语言Verilog HDL。组合系统的解算由PC104完成,对PC104的软件设计采用C语言在DOS系统下在Turbo C中编写,导航解算应有不同的解算周期。因此,导航计算机系统软件设计分为FPGA软件和PC/104主控系统软件两部分。

评论