基于Wishbone和端点IP的PCIE接口设计

DMA写操作实现的主要方法是主机将TLP包头中的各个字段正确填充,按照32位并组装成TLP包头,通过主机PCI Express接口传输到集成端点硬核。硬核收到数据后,缓存到Rx_ram中,在解码逻辑控制下,根据包头类型(10/11b)及格式字段(00000b)发起Wishbone写操作,将TLP包的有效载荷写入存储器中。

在进行PCI Express的DMA读操作时,数据通过wishbone总线读入,在编码逻辑控制下,数据按照TLP包格式写入Tx_ram中,将数据打包成一个3DW完成包,等待端点模块发送。

2.3 功能仿真

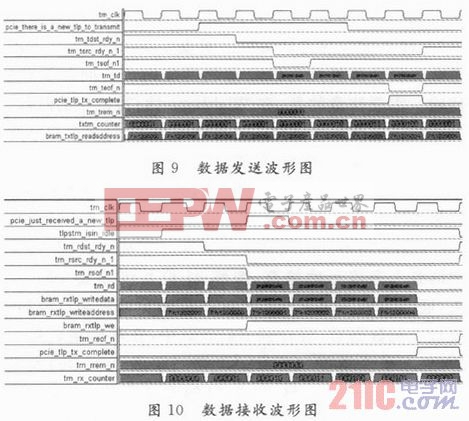

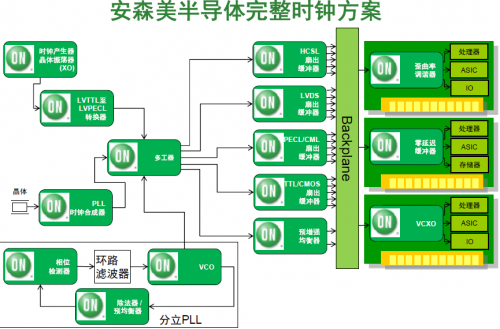

本设计在XUPV5 LX110T开发板上进行了功能验证试验。首先利用Xilinx公司的CORE Generator工具生成PCI Express端点IP核,其主要参数是链路数为X1,基地址0使能,地址类型为32位,访问类型为Memory类型,用户时钟输入为62.5 MHz。编程设计完成后,通过JTAG接口下载到FPGA芯片中,用Chipscope进行测试,波形图如图9~图10所示。本文引用地址:https://www.eepw.com.cn/article/190176.htm

通过数据传输试验测试,Wishhone转PCI Express接口的传输速率能达到80 MB/s以上,系统工作稳定。目前,Wishbone实现了32 b/16 b/8 b的单个存储器的读和写和DMA读写。如能够编程实现Wishbone大字节块的突发传输,传输速率将大大提高,这也是下一步开发的重点。

3 结语

测试试验结果证明,采用Wishbone和端点IP实现PCI Express总线接口,具有较高的通信速率,能满足许多应用的一般通信要求,特别是开发过程简化且极大地缩短了开发时间。这种设计模式能够更加专注于应用功能的实现而不必在一些公共模块(如PCIExpress)上花费更多的时间和成本。另外,本文采用FPGA芯片内嵌PCI Express End point Block硬核来进行PCI Express的设计,实现方式也为相似产品开发提供了有益参考。

评论