基于DDS IP核及Nios II的可重构信号源设计

2.4 波形选择模块的设计

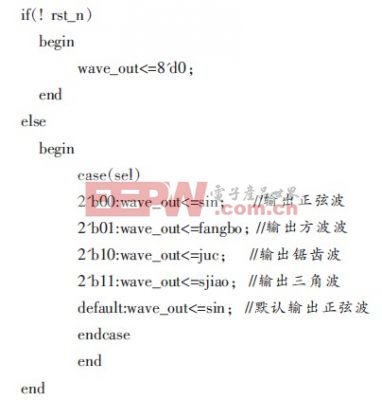

该模块根据DDS控制模块的输出控制信号决定选择哪一种波形输出,关键代码如下。

2.5 DDS顶层设计

顶层设计将前面实现的各功能模块作为底层元件例化调用,完成整个DDS IP核设计。对DDS IP核进行验证后,利用SOPC Builder的组件编辑器对其进行自定义组件的开发,为后续SOPC硬件系统的搭建奠定基础。

2.6 DDS IP的仿真测试及自定义组件的生成

Altera公司的Quartus II软件具有嵌入式逻辑分析仪SignalTap II,它提供了一种对器件进行实时测试的手段。SignalTapII嵌入式逻辑分析仪可以随设计文件一起下载到目标芯片中,用以捕捉目标芯片中设计者感兴趣的信号节点处的信息,而不影响芯片的正常工作。

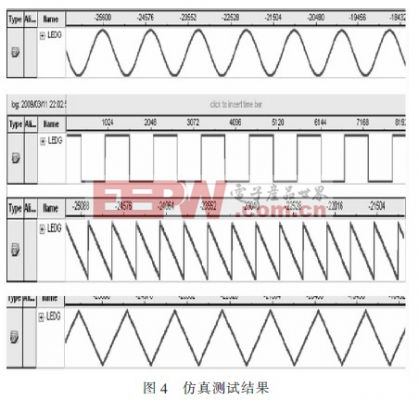

SignalTapII将测得的样本信号暂存于目标器件的片内RAM中,然后通过器件的JTAG端口和编程线将采得的信息传出,送入计算机进行分析。图4是采用SignalTapII嵌入式逻辑分析仪的仿真测试结果。

由于SOPC的开发是以组件(IP核)为基础的,为了将前面设计的DDS IP核挂到Avalon总线上,将其封装成为SOPCBuilder自定义的组件,如图5所示。这样,在SOPC硬件系统开发中,DDS IP就如同SOPC Builder里的标准组件一样,可以被集成到具体的应用系统中。

评论