基于UART的智能卡接口IP核设计

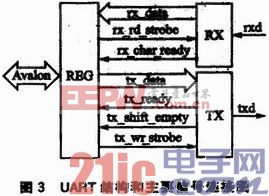

UART核主要有三大模块;发送模块(TX)、接收模块(RX)、寄存器模块(REG)。与CPU连接端为Avalon总线接口,与外部连接端为txd和rxd其主要结构和信号连接如图3所示。本文引用地址:https://www.eepw.com.cn/article/189738.htm

REG模块通过tx_wr_strobe把数据tx_data写到TX模块中,TX模块按照设定的波特率往txd串行发送数据,同时把发送寄存器和发送移位寄存器的状态通过tx_ready和tx_shift_empty传回REG模块。

RX模块根据设定的波特率对rxd进行采样接收,当接收到1字节有效数据时置rx_char_ready有效,REG模块通过rx_rd_strobe读取接收的数据。

REG模块中包含控制寄存器、状态寄存器、波特率寄存器、数据寄存器,还包含Avalon总线接口逻辑以及各种寄存器的操作逻辑。

2.2 智能卡接口IP核结构设计,

智能卡的引脚有电源、地、复位、时钟、数据,其中只有复位和数据线与操作有关,因此在IP核中只需要复位线和数据线。

智能卡操作过程中,接收的数据和发送的指令都需要哲存在IP核内,因此要在UART核上增加发送和接收缓冲。除此之外,还需要增加协议处理模块用于操作过程中的判断和交互,增加收发切换模块实现异步半双工的切换,增加发送控制模块用于发送不同的数据。基于UART核的智能卡接口IP核结构如图4所示。

图4中,保留UART的RX和TX模块不变,在REG模块中增加了RX_BUF、TX_BUF、缓冲区长度寄存器,还增加了清缓冲区等功能。

在UART核的基础上增加协议处理模块,它是操作智能卡的核心。协议处理模块从RX模块直接截取数据并处理,根据流程进行各种操作。协议处理模块可以清除接收缓冲区中的过程数据、清除无效的发送指令,协议处理模块还控制收发的切换、控制发送指令、控制IC卡复位。

发送控制根据协议处理中的状态和命令,发送不同的指令到智能卡中。

2.3 协议处理的实现

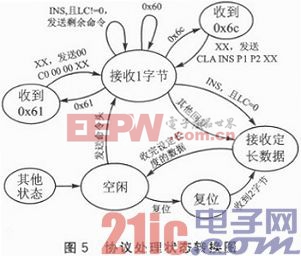

在图4中,协议处理模块是实现CPU与智能卡交互的关键,本文采用状态转换的方法来实现。根据复位操作(图1)和指令操作(图2)的流程,可将智能卡的操作总结为7种状态:空闲状态、复位状态、接收1字节状态、接收定长数据状态、收到0x61状态、收到0x6c状态、其他状态。状态转换的主要条件是接收到特定的数据或接收到特定个数的数据,辅助条件是当前的状态和其他参数。状态转换图如图5所示。

空闲状态:刚上电或无操作时处于空闲状态,IP核等待CPU的命令。

复位状态:在空闲状态下收到复位命令后,复位智能卡并进入复位状态,等待接收数据。根据前2字节的回复设置接收数据长度,然后进入接收定长数据状态。

接收定长数据状态:根据前一状态的设置,等待接收固定个数的数据,当接收到设定个数的数据时,向CPU发送中断请求并跳转到空闲状态。

接收1字节状态:在空闲状态下当有效指令操作下发时,发送5字节命令头,进入接收1字节状态。在该状态下,收到0x60则不进行任何处理;收到INS时需判断LC,若LC不为0则发送剩余指令,若LC为0则设置接收长度进入到接收定长数据状态;接收到0x61或0x6c则分别进入到相应状态;接收到其他回复则设置固定接收长度为2,并进入接收定长数据状态。

收到0x61状态;接收1字节数据为0x61时进入该状态,在该状态下等待接收1字节数据并将该数据加到00 C0 00 00后一起发送,同时回到接收1字节状态。

收到0x6c状态:与收到0x61过程基本一样,将接收到的数据加到CLA INS P1 P2后面发送。

设计时,在非空闲状态下设定超时计数器,计数器溢出后无条件返回到空闲状态,同时清除接收和发送缓冲,表示本次操作失败。另外,所有的过程字节在状态处理时都被清除。

评论