基于CMOS阈值电压的基准电路设计

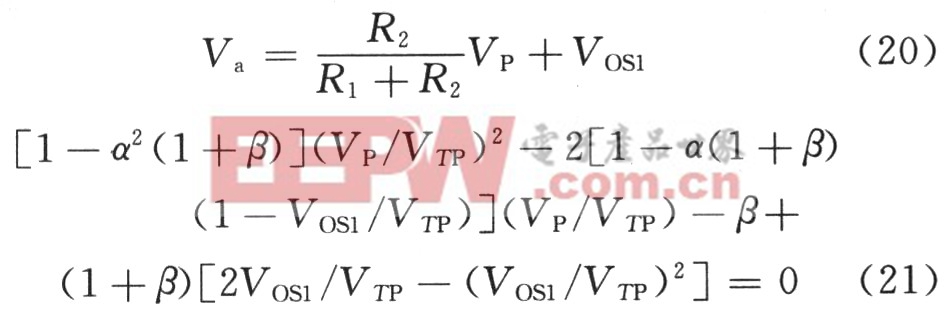

由于工艺及实际生产中存在偏差,运放通常会受到输入“失调”的影响。假设失调电压为Vos,以A1为例,原来的式(10)与式(12)变为:

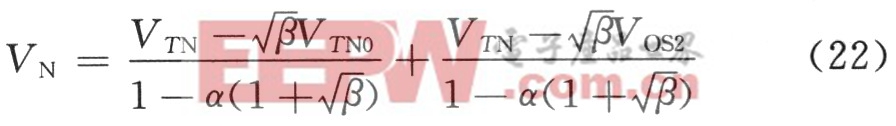

因为VOS1《VTP,所以含有VOS1的多项式的值也很小,其对于VP的影响也小。同理对A2,A3,式(17),式(18)变为:

同样,由于VOS2《VTN,VOS3《VP,所以A2,A3的失调电压对于VN和Vref的影响也很小,并且,其对于Vref的作用还可以通过R7/R5来补偿。

3 电路设计

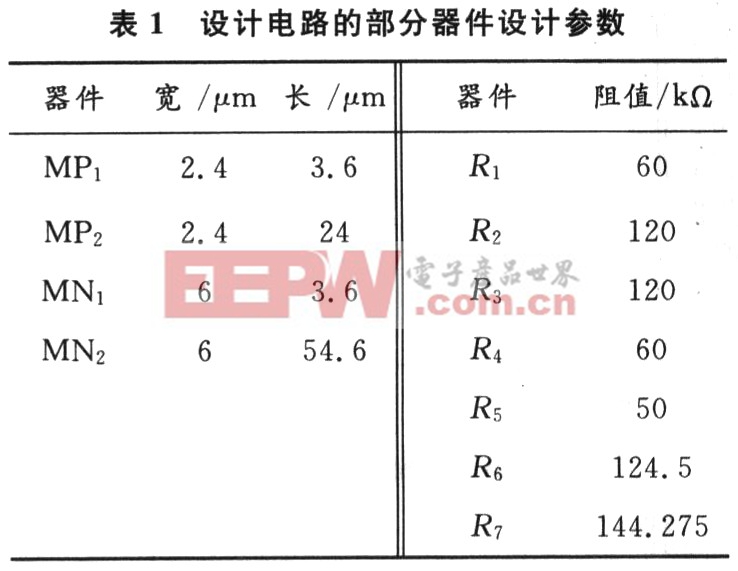

基于上面分析,该电路基于某公司O.5 μm工艺设计,表1所示的是图3中部分器件的设计参数。

为了减小运放的失调电压,MP1,MP2对和MN1,MN2对均采用相同的宽度以确保较好的匹配性。另外,由式(11)、式(16)分析可以看出,阈值电压也需要一定的匹配,因此设计中使用一些大尺寸的器件,并在版图中将它们放置在相邻的位置,以消除失调。

4 仿真结果

根据以上电路设计,电路采用hSpice进行仿真验证。如图8(a)~(c)所示分别为该电路输出O.6 V,1.2 V以及2.95 V的仿真结果。可以看出,在-50~+125℃之间,输出的基准电压只有零点几个毫伏的波动,明显降低了传统电路中由于双极晶体管带来的温度系数,并且输出并不再像带隙基准那样,只能输出l.25 V的基准电压,而是可以通过调整减法器的比例来达到设计者需要的基准电压。

5 结 语

依据CMOS阈值电压和温度的线性关系,利用阈值电压产生两个独立于电源电压和晶体管迁移率的负温度系数电压VP和VN,通过将其相减,抵消温度系数,从而得到任意大小的基准电压值。设计电路中不涉及双极晶体管,从而避免了其带来的温度影响。电路基于某公司O.5 μm CMOS工艺设计,利用HSpice进行仿真验证,各项指标均已达到设计要求,并已成功应用于一款高精度的ADC电路中,且实际测试结果与设计值吻合,验证了该方案的正确性与可行性。目前正在将其应用于锁相环等电路中,使该基准电路得到更广泛的应用。

评论