5.6GHz CMOS低噪声放大器设计

摘要:分析了一种射频COMS共源-共栅低噪声放大器的设计电路,采用TSMC 90nm低功耗工艺实现。仿真结果表明:在5.6GHz工作频率,电压增益约为18.5dB;噪声系数为1.78dB;增益1dB压缩点为-21.72dBm;输入参考三阶交调点为-11.75dBm。在l.2V直流电压下测得的功耗约为25mW。

关键词;互补金属氧化物半导体;低噪声放大器;噪声系数;线性度;

0 引言

低噪声放大器(LNA)是射频接收机前端的主要部分。它主要有四个特点:首先,它位于接收机的最前端,这就要求它的噪声越小越好。为了抑制后面各级噪声对系统的影响,还要求有一定的增益,但为了不使后面的混频器过载,产生非线性失真,它的增益又不宜过大。放大器在工作频段内应该是稳定的。其次,它接受的信号是很微弱的,所以低噪声放大器必定是一个小信号线性放大器。第三,低噪声放大器一般通过传输线直接和天线相连,放大器的输入端必须与其有很好的匹配,以达到最大传输功率或最小的噪声系数。第四,应具有一定的选频功能,抑制带外和镜像频率干扰。

在GHz频率范围内,CMOS工艺相比其他工艺有价格低、集成度高、功耗低等优点,利用CMOS工艺来设计射频集成电路已经得到越来越广泛的应用,本文即采用CMOS工艺来实现对一种5.6GHz低噪声放大器的设计。

1 LNA结构及性能分析

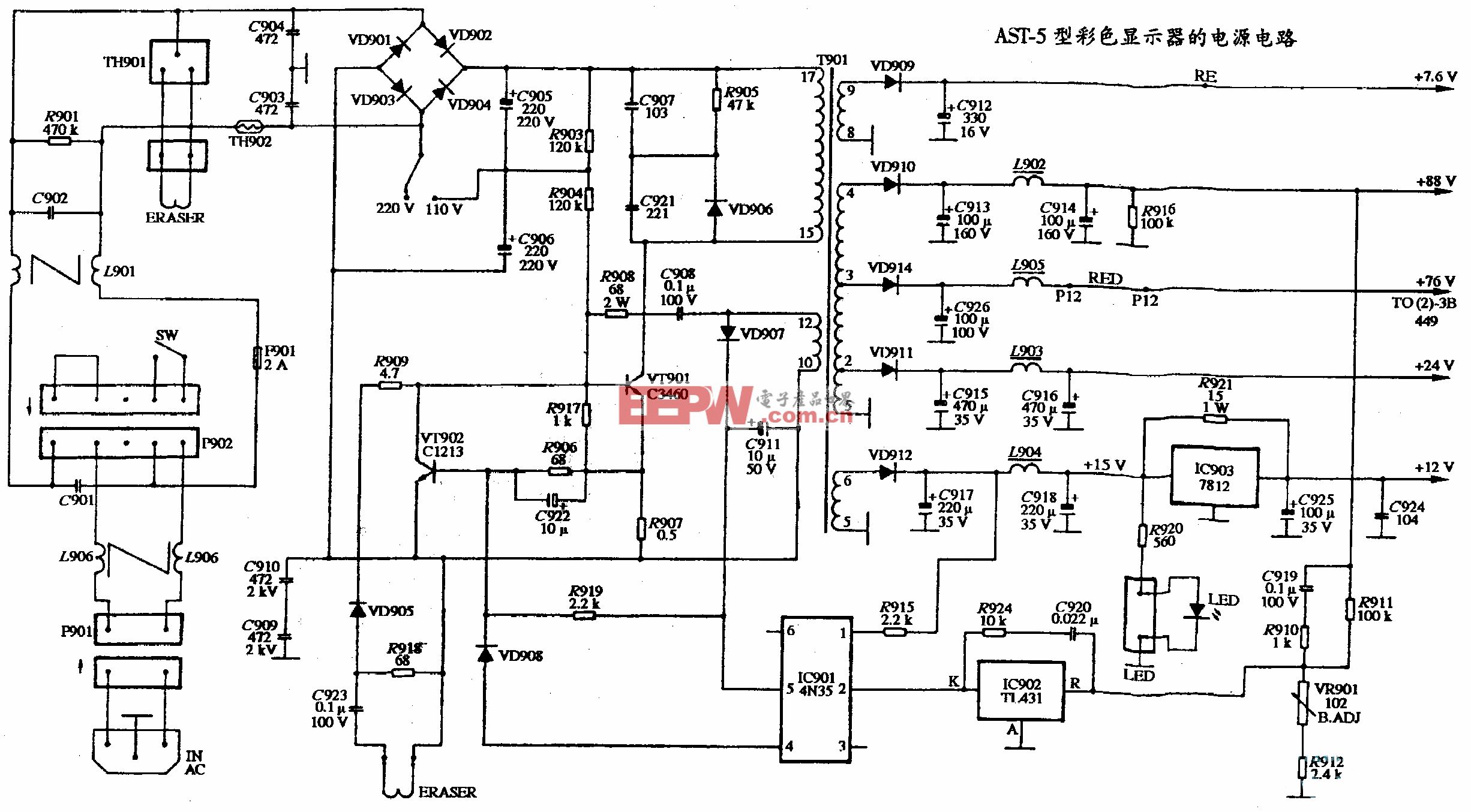

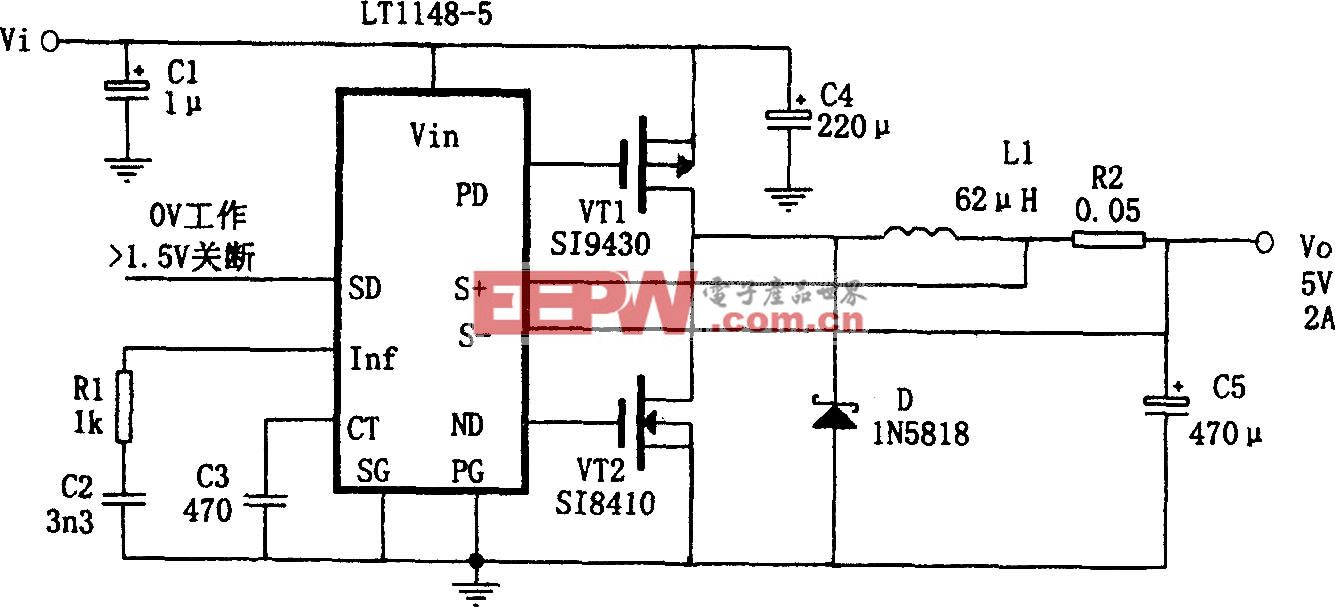

由于带源端负反馈电感的共源放大器具有噪声系数低、增益高、线性度好,以及可实现输入阻抗匹配等优点,因此在无线收发机系统中得到广泛应用。为了减小晶体管的Miller效应和有限输出阻抗对放大器性能的影响,并提供良好的方向隔离性能,低噪声放大器通常采用Cascode结构。具体电路如图1所示。

共栅方式连接的晶体管M2用来减少调谐输出与调谐输入之间的相互作用,并同时减少Ml的Cgd的影响。晶体管;M3基本上是与M1形成一个电流镜,通过M3的电流是由电源电压和Rref以及M3的Vgs决定的。电阻RBIAS选择得足够大,所以它的等效噪声电流小到足以被忽略。为了完成偏置,必须用一个隔断DC的电容CB来防止影响M1的栅源偏置。

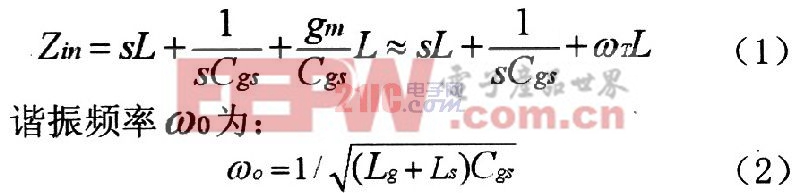

M1源级接Ls,形成源级负反馈结构,栅极接Lg,做输入匹配使用。若忽略栅漏电容Cgd,则其输入阻抗可以表示为:

其中Lg、Ls为片上平面螺旋电感。为了实现50Ω阻抗匹配,通过调谐感抗,使其在谐振频率ωo处谐振,上式的虚部为零,实部等于50Ω。这种匹配设计的好处在于使用等效电阻![]() 实现与输入端的匹配,而无需引入实际电阻,因而减少了额外的热噪声。即如下式:

实现与输入端的匹配,而无需引入实际电阻,因而减少了额外的热噪声。即如下式:

这就是源极负反馈结构在LNA设计中普遍采用的一个原因。在设计过程中,由式(3)根据M1的参数和50Ω匹配条件设计出Ls,再由式(2)根据工作频率点和滤波要求确定栅极电感Lg。

评论