基于折叠结构的半带滤波器的设计

3 仿真与实现本文引用地址:https://www.eepw.com.cn/article/187587.htm

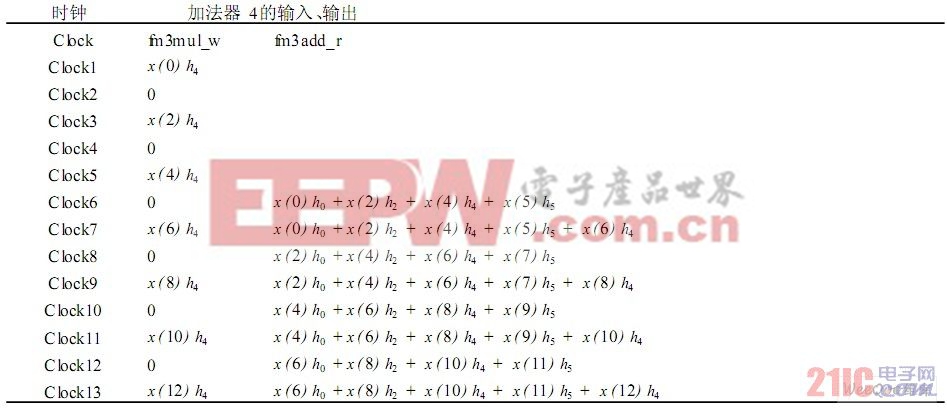

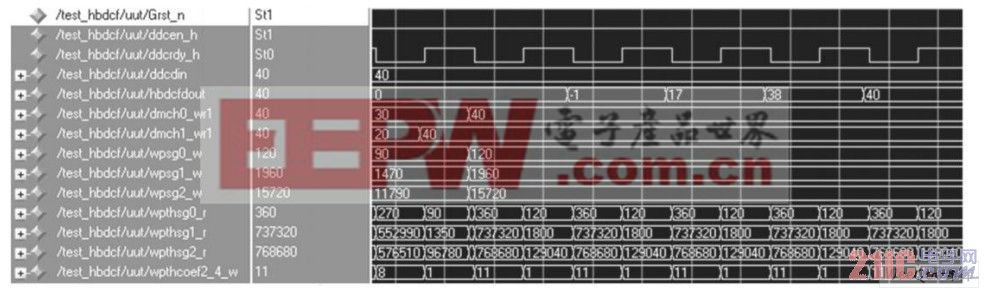

本设计采用Verilog语言编写,所采用的芯片是Xilinx公司的xc4vsx35 - 10ff668,用ISE10. 1和Modelsim进行仿真验证。仿真结果、综合报告图如图3、图4所示。从图3我们可以看出采用折叠技术的半带滤波器,其系数的产生以及最终滤波器的输出完全正确,完全满足我们的设计要求。

传统的直接型半带滤波器的设计单单滤波过程,不包括系数的产生和抽取过程,需要10个D触发器、7个乘法器、6个加法器,而转置型半带滤波器则需要10个D 触发器、4 个乘法器、7 个加法器。

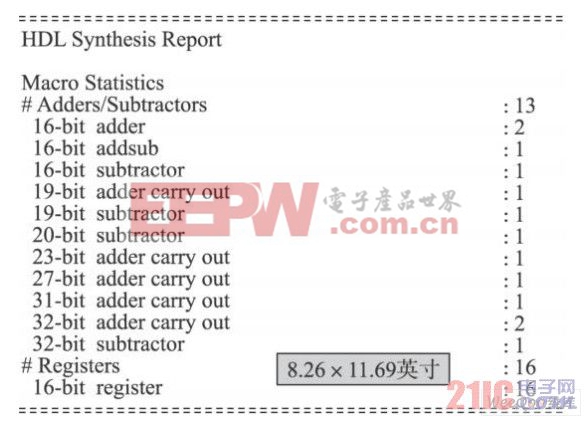

然而从图4我们可以看到整个半带滤波器耗费的资源相当的少,总共用了13 个加法器, 16 个寄存器。而由此可见采用折叠结构实现半带滤波器的设计能够大大减少资源的耗费,而且整个过程没有用到乘法器只是用到少量的加法器和寄存器,减少了大量的乘法带来的额外的面积和功耗。同时本设计还经过硬件电路的验证,工作正常稳定,符合设计要求。

图3 基于折叠结构的11阶半带滤波器仿真图

图4 基于折叠结构的11阶半带滤波器综合报告图

4 结论

本文以11阶半带滤波器的设计为例,介绍了折叠技术在半带滤波器上的应用。与传统的设计相比其有很大的优越性和突破,单一时钟控制,并且设计过程当中没用到乘法器,大大减少了硬件资源,同时也使设计面积和功耗大为减少,稳定性高!

评论