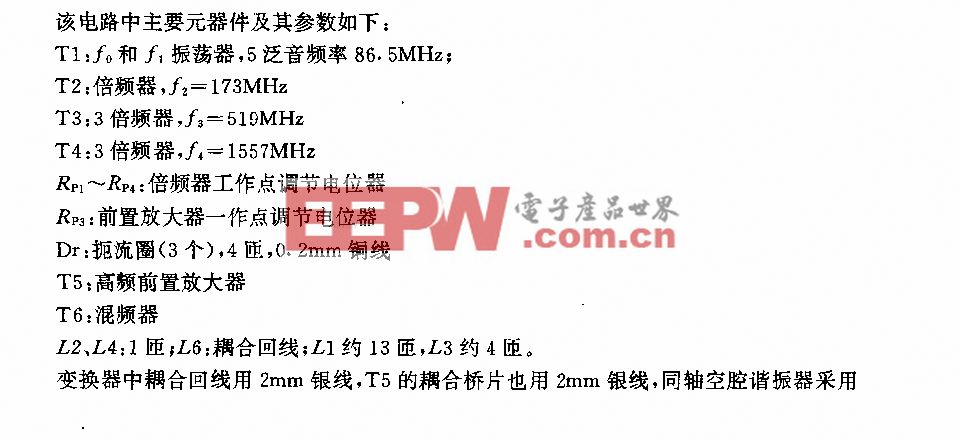

基于ADS的接收机码元同步算法实现

2、改变VCO的预设基本频率 来仿真接受端时钟偏差,VCO的敏感度S为1MHz/V。

来仿真接受端时钟偏差,VCO的敏感度S为1MHz/V。

仿真结果:

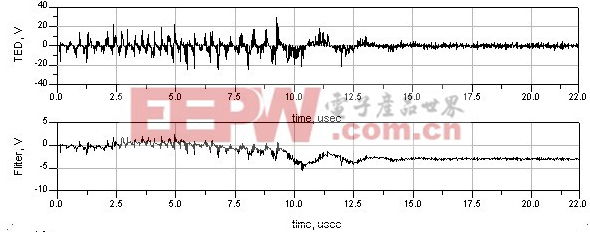

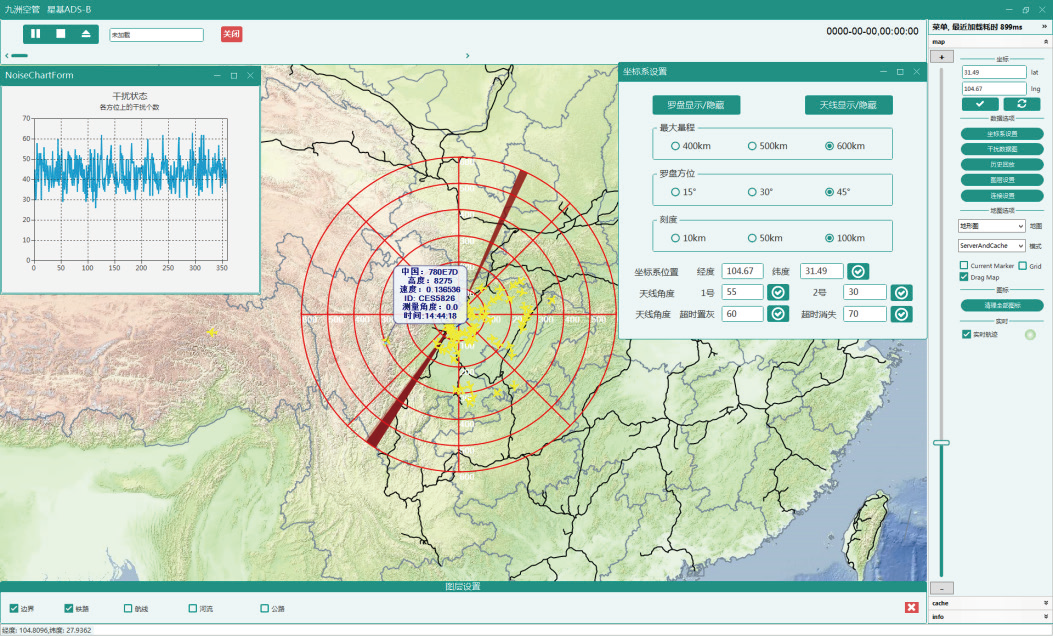

图6 时钟恢复环中误差信号、环路滤波后的信号

图6为从码元同步模块中测量出来的误差信号、环路滤波后的信号。从图中可得出,VCO根据反馈回来经过滤波后的误差信号(如图6下)来实时调整采样的频率,直到VCO输出时钟频率 等于2倍码元速率为止,就达到了平衡状态,此时定时误差为零(如图6上)。

等于2倍码元速率为止,就达到了平衡状态,此时定时误差为零(如图6上)。

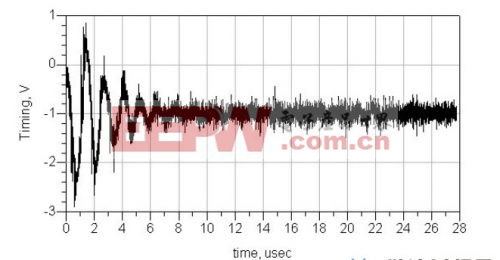

图7 不同码元速率的锁定过程

图 7所示分别为1.8GHz采样率,码元速率720Mbps,初始偏差1MHz,信噪比20dB时码元同步的锁定情况;和0.9GHz采样率,码速率 360MHz,初始偏差1MHz ,信噪比20dB时码元同步的锁定情况。仿真证明这种码元同步方法能够正确生成码元时钟满足高码速要求,并且适应不同码速率。能正确生成码元时钟满足高码速要求,并且适应不同码速率。

| 测试环境 测试项目 | 无码元同步模块时误码率(BER) | 有码元同步模块时误码率(BER) | |

| 理想系统 | 4.554E-6 | 4.554E-6 | |

| 抖动 | 8.730E-5 | 9.039E-6 | |

接收时钟偏差 | Bias=0.5MHz | 0.017 | 4.554E-6 |

| Bias=1MHz | 0.036 | 4.554E-6 | |

| Bias=1.5MHz | 0.041 | 4.554E-6 | |

| Bias=2MHz | 0.054 | 0.065 | |

| 抖动和偏差 | 0.048 | 1.937E-5 | |

表1 仿真系统中的码元抖动、时钟偏差时的误码率

通过上表说明,如图5所示的系统中,码元同步模块对于的信号的抖动和接收端时钟的频率偏差有较强的纠正能力。抖动为半个码元长度时,模块将误码率从 1.730E-5降到了9.039E-6。对于时钟的频率偏差纠正能力尤为突出,达到3MHz的范围(748.5MHz~~751.5MHz)内都可以锁定。当同时加入码元抖动和时钟偏差时,系统也表现出了较强的纠错能力。

3 结束语

本文简要介绍了在ADS仿真器中,设计一个16QAM接收机的码元同步模块,以消除恢复时钟偏差和I、Q两路信号的不同步引起的码元抖动的问题。并针对16QAM这种调制方式,提出了改进的误差提取算法。仿真显示可以满足不同速率下的接收机要求。

评论