基于全耗尽平面晶体管技术的NovaThor平台设计

因此,在宽Vdd电压范围(0.5V 至 1.3V)内,FD-SOI的综合性能高于移动处理器专用的体效应CMOS工艺,这些性能优势可用于提高峰值性能,或者在保证性能不变的前提下降低Vdd工作电压,从而降低动态功耗。

我们探讨了FD-SOI工艺在性能-电压比方面的技术优势,接下来,我们将分析另外两大优势:具有竞争力的处理速度/泄漏电流比和优化能效。

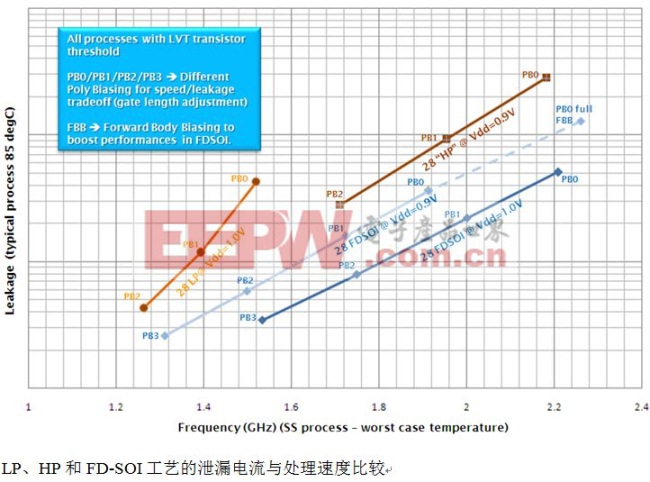

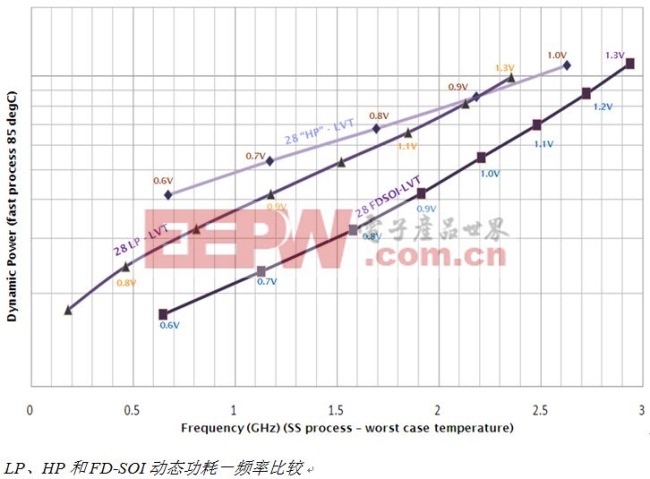

具有竞争力的处理速度/泄漏电流比 FD-SOI工艺不仅带来前文所述的性能优势,还具有同级产品最低的泄漏电流,下图示是前文图示的ARM Cortex-A9 关键通道在85°C时典型泄漏电流与最高频率之比。以系统的方法分析,当泄漏电流相同时,FD-SOI在标称电压(1.0V)时的运行频率高于标称电压(1.0V)时的LP工艺或标称电压(0.9V)时的HP工艺。 浅蓝色曲线代表Vdd=0.9V条件下的FD-SOI 泄漏电流/速度曲线,这意味着FD-SOI可让我们降低标称 Vdd 电压(对动态功耗影响巨大的参数),同时保持与LP和HP工艺相同的或更高的性能。然后,如蓝色延长虚线所示,施加在LVT FD-SOI晶体管上的正向体偏压(*) 使其能够达到HP可达到的性能,而在施加偏压后,多晶硅晶体管的泄漏电流增幅与LP工艺相同。 该泄漏电流/速度比优势是28nm FD-SOI工艺独有优势,真正地融LP 和 HP两大工艺的优点于一身。 体偏压是在CMOS晶体管的体效应部分施加可变电压,以提高泄漏电流为代价换取更快运行速度(正向体偏压),或者以牺牲性能为代价换取更低的泄漏电流(反向体偏压)。虽然体效应CMOS具有这项功能,但是,因为埋沟氧化层将晶体管沟道与硅体效应部分(背栅效应)隔离,体偏压的效果在FD-SOI技术上更加出色。 优化能效 对高端移动应用来说,良好处理性能兼出色的泄漏电流还不够,在移动设备日常使用过程中降低不同工作模式的总功耗才是最大化电池续航能力的关键。 下图描述了三种不同的 28nm 工艺的动态功耗特性,并给出了动态功耗-最大频率特性曲线。 从图中不难看出,在给定频率时,FD-SOI的总功耗总是比其它两项技术低很多,即便达到目标频率所需的电源电压略高于28nm HP.这主要因为FD-SOI技术的总功耗中泄漏电流较低。在整个电源电压范围和对应的性能范围内均是如此,这充分证明,FD-SOI是能够给移动设备带来最高能效的解决方案。 从上文可以看出,28nm FD-SOI在对于移动计算设备极其重要的关键参数方面优于现有的体效应工艺,具有高性能且低功耗的优点。

评论