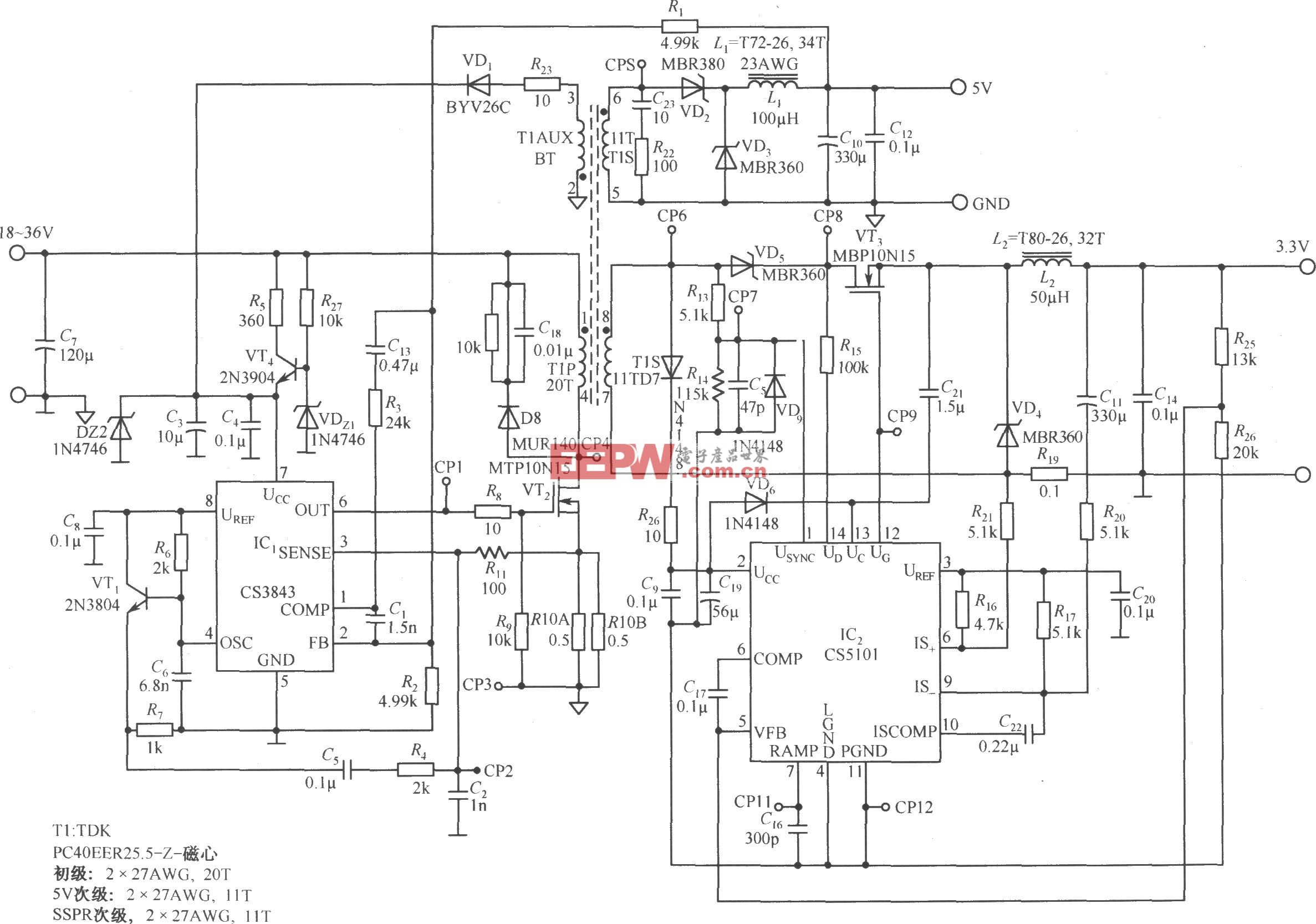

功率因数校正(PFC)的数字控制方法

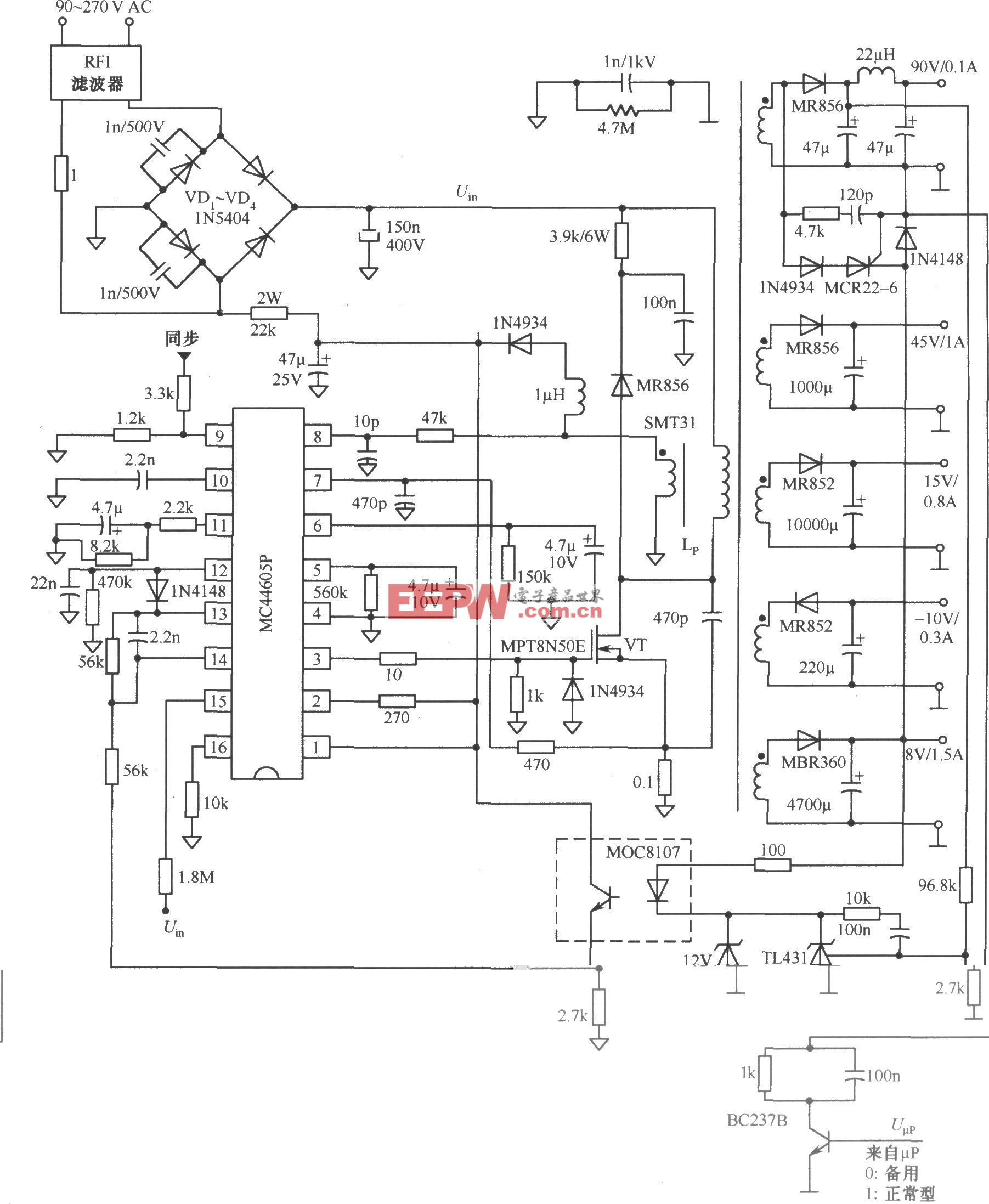

数字控制器包括一个电流环和一个电压环。对于电流环,将指令输入电流减去输入电流iL,n所得的电流误差ie,n输入到电流环数字PI控制器。最后,将控制器输出的占空比Dn输入到PWM产生单元,控制开关S的通断。对于电压环,PFC变换器的输入电导期待值ge,n与输入电压vin,n相乘,得到指令输入电流iL,n*。

2 数字控制的实现

在实现一个电力电子系统的实际数字控制器时,需要考虑大量的因素,比如,控制处理器的选择,采样算法和采样频率的确定,PWM信号的产生,控制器和功率电路之间的连接,硬件设计和控制算法的软件实现等。这些因素都会对系统的性能产生很大影响,需要细心设计和实际实验。

2.1 微处理器的选择

在设计控制系统时,微处理器的选择需要考虑很多的因素,诸如功能,价格,硬件设计的简单性和软件支持等。现在,已经有多种内嵌有PWM单元和A/D转换等控制外设的DSP芯片可供选择(比如TI的TMS320C2XX系列,AD的ADMCXXX系列,Motorola的DSP56800等)。以TI公司的TMS320C2XX系列为例,它拥有很多良好的特性,比如,多个独立可编程的时钟,50ns指令周期,16位并联乘法器,两通道多路复用的10位A/D转换器,还有片内RAM和EEPROM等。这使得它成为实现功率变换系统数字控制的首选。如果需要进一步降低成本,可以选择STmicro-controller的8位DSPST52x420。

2.2 采样算法和采样频率的选择

在设计数字控制器时,选择合适的采样频率起着重要的作用,因为,采样频率直接影响到可完成的功能和数字控制系统的可靠性,因此,它应该在合成控制器之前确定。对于更高的系统带宽要求,应该使用更高的采样频率。然而,采样频率的提高也对字长和数字控制器的计算速度提出了更高的要求。工程设计的目标总是使用更低的采样频率来达到给定的设计要求。

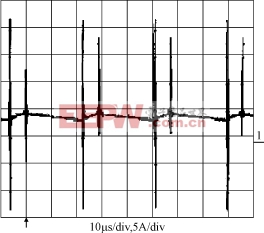

由于Boost变换器的输入电流含有大量谐波。因此,采样频率必须远高于开关频率,输入电流才能不失真地还原。由于开关频率已经很高(>20kHz),要采用更高的采样频率是困难的,而且,处理器也来不及处理相应的控制计算任务。而使用比较低的频率将产生频谱重叠。虽然可以在A/D转换前加入前置滤波,但是,这样又需要更高的带宽。因此,采样频率选择与开关频率同步,这样,开关纹波就成为隐性振荡,不会在还原信号中出现。这种采样方法在一个周期中只采样一次,称为SSOP(single sampling in one period)方法。采用这种采样方法时,有一个采样点确定的问题。电感电流在开关的瞬间存在电流尖峰,如图3所示。显然,应该避免在开关点进行采样,否则系统将不能正常工作。在PFC应用中,输入电流必须跟踪输入电压,而且输出电压要保持恒定,PWM信号将在一个大的范围内变动,因此,这个问题变得更加突出。

图3 存在高频噪声的电感电流

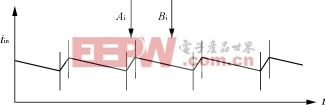

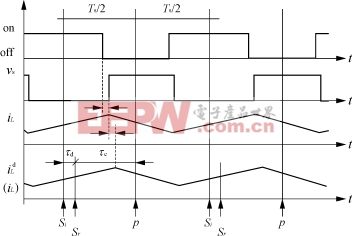

为了保证在每次开关周期中确定一个固定的采样点,而且远离开关点,一个简单的设想就是在两个尖峰之间(上升沿或者下降沿)的中点进行采样,即采样平均电流。但是,当上升沿或者下降沿非常窄的时候(即开关的占空比非常窄或者非常宽),采样信号的准确度仍然会受到开关噪音的影响。如图4所示,如果采用上升沿采样,当导通时间较长时〔图4(b)〕,采样点(Ai)是可靠的,反之是不可靠的〔图4(a)〕。为了克服这个缺点,采用改进的采样算法。这个算法同样是同步采样,但是,采样边沿的选择取决于开关的导通时间。如果导通时间大于关断时间,选择上升沿;反之采用下降沿。这样便很好地避免了开关噪声的影响。而且算法本身简单,计算量少。如图5所示。

(a) 导通时间短

(b) 导通时间长

图4 输入电流波形

![]()

(a) 导通时间关断时间

(b) 导通时间≈关断时间

(c) 导通时间>关断时间

图5 改进采样算法的采样瞬间

2.3 PWM信号的产生

为了叙述方便,定义一个开关周期的起点p,如图6所示。对大多数数字PWM单元来说,占空比的值应该在开关周期开始之前装载入寄存器,因此,控制变量的采样应该在p点之前准备好,以便控制算法的计算及时完成。这里采用平均电流控制,选择采样点,得到每个开关周期的输入平均电流测量值。

图6 开关指令和测量输入电流iLd之间的延迟

注:信号从上至下分别为:开关指令,开关S两端的电压vs,输入电流iL,测量输入电流iLd。

理想的采样点si和实际采样点sr之间有一个时间延迟τd。τd由两个原因造成,一个是在信

号链中低通滤波器产生的相移,另一个是开关S的开关指令和实际开关动作之间的延迟。这样,留给处理器完成控制计算的时间就是τc。延迟τd和计算时间τc共同决定了反馈环路的延迟。

gd(s)=![]() =

=![]() (1)

(1)

式中:Ts为开关周期。

使用顶点规则采样PWM方法产生开关指令。如图7和图8所示。对于输入信号u在平衡值附近的小偏移,顶点规则采样PWM的响应可以描述为

评论