高速CMOS钟控比较器的设计

2. 2 失调电压

比较器的失调电压主要来源于预运放的失调电压。它主要是由MOS管阈值电压的失配和电流的失配引起的,它的标准差如下式:

其中:

式中,δ21, 2是预运放输入差分对失调电压的标准差,δ23, 5是预运放负载管失凋电压的标准差; AVTN , AVTP ,AβN , AβP分别是NMOS管和PMOS管工艺模型中阈值电压的失配因子和电流的失配因子。从式( 6) 、(7) 、(8)可以看出,减小预运放输入差分对管和负载管的过驱动电压,并适当增加它们的面积可有效地减小输入失调电压。但同时增大了漏极电容,降低比较器的速度。因此,比较器的设计需要在功耗、速度和精度之间进行折中。

3 电路仿真

通过以上分析,使用Hsp ice进行仿真与优化,最终确定比较器的核心电路(预运放与判断级电路)内各晶体管尺寸如表1所示。

表1 比较器核心电路各晶体管的宽长比

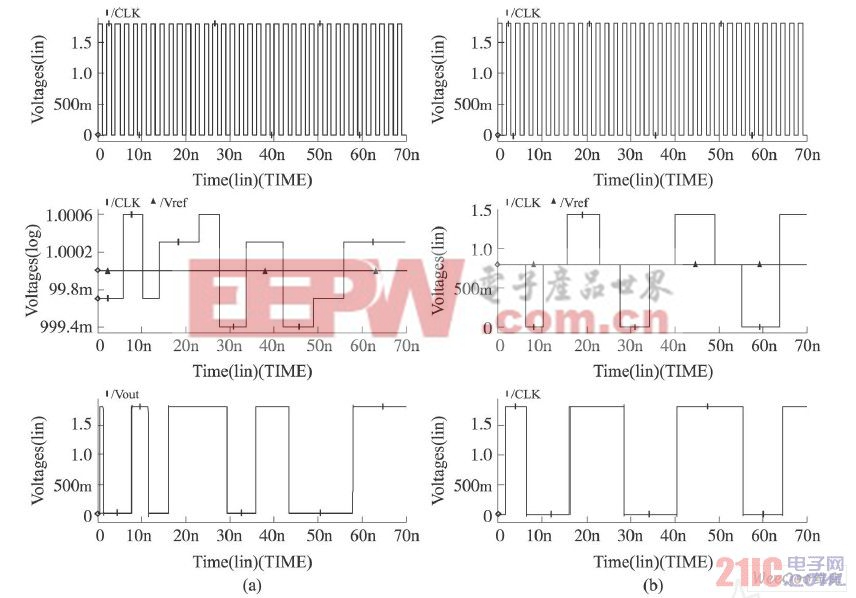

在电源电压1. 8 V、SM IC 0. 18μm CMOS工艺模型下,采用Hsp ice对前面设计的比较器电路进行仿真。为了检验比较器在各种工作情况下输出的正确性,在比较器的输入端加上幅度和极性随时间变化的信号作为测试信号,工作时钟频率为500MHz,仿真波形如图6所示。图6 ( a) 、( b)中第一栏是时钟控制信号CLK,第2栏是输入信号Vin和参考电压Vref ,第三栏是比较器的输出信号Vout。通过对仿真结果进行分析,在输入信号为具有大跳变极端信号(在基准参考电压0. 8 V 下,两信号为0. 81、0 V或是0. 79、1. 8 V)的情况下,比较器的最小精度为±0. 3 mV (基准电压1 V) ,仿真结果验证了比较器功能的正确性。

图6 比较器整体仿真波形

4 结论

本文设计了一个基于1. 8 V电源电压、时钟频率可以达到500MHz的高速钟控电压比较器,采用预放大级、判断级、输出缓冲级结构,每一级的电路结构简单,通过对各个部分电路的特点进行分析,优化了前置放大器的晶体管的尺寸,实现了高速、高精度、低功耗的要求。在SMIC 0. 18μm CMOS工艺模型下,采用Hspice对电路进行仿真,结果表明在500 MHz的时钟频率下,比较精度可达0. 3 mV,功耗仅为26. 6μW,该电路可以应用在高速Flash ADC电路中。

评论