基于VHDL的异步FIFO设计

仔细观察表1并分析数据,一种新颖的判断空满标志的方法为:当读/写指针的最高位(MSB)不相等且读/写指针的次高位不相等,剩余的N-2位地址相等时,此时写指针追上了读指针,即写指针比读指针多转一圈,状态模块输出满标志;当读/写指针N+1位都相等时,状态模块输出空标志。判断满标志部分的VHDL代码:

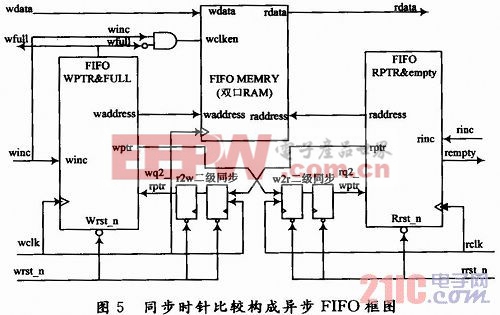

3.4 异步FIFO总体设计

通过时针比较产生的异步FIFO框图如图5所示。WCLK和RCLK分别为读时钟和写时钟,wrst_n和rrst_n分别为读/写模块的复位信号。 rdata为数据输出端口,wdata为数据输入端口。异步FIFO通过读/写指针来寻址一个双口RAM来实现对数据的读/写,双口RAM的大小为2nB。读指针被二级同步链到写时钟域,然后与写时针比较产生满标志,读指针产生读地址raddress;写时针被二级同步链同步到读时钟域,然后与读时钟比较产生空标志,写指针产生写地址waddress。需要注意的是此异步FIFO设计中,空满标志是保守的空满标志,比如满标志,当读时针通过二级同步链同步到写时钟域且满足满标志的条件时,写指针停止加1操作,而同步读指针的过程中,读时针则移动到了其他的地址,同样的适合于空标志,当输出空,满时,其实FIFO的真实状态是还有空间没被写满或者读空,这就是保守的空和满,而这正保证了FIFO不会向上会向下溢出,进一步提高了FIFO工作的可靠性。本文引用地址:https://www.eepw.com.cn/article/178738.htm

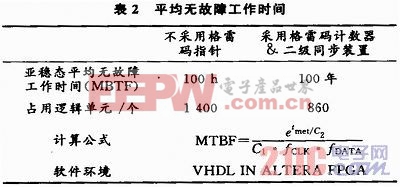

表2为平均无故障工作时间的对比,C1和C2依赖于器件工艺。

4 结语

一个高的平均无故障工作时间表明一个设计是优秀的,提高亚稳态的平均无故障工作时间减少信号传输中导致亚稳态问题的风险。本文通过研究FIFO的基本结构以及FPGA亚稳态的产生机理,提出了利用二级同步链和格雷码计数器指针解决了同步以及空满状态判断的难题,给出了VHDL软件代码,且该设计已经通过QuartusⅡ的时序仿真验证,作为独立模块可以应用到需要异步时钟域传输数据的电路中,大大提高异步数据传输效率及平均无故障工作时间。

评论