应用于负电源的电平位移电路及器件设计

2 器件设计及优化

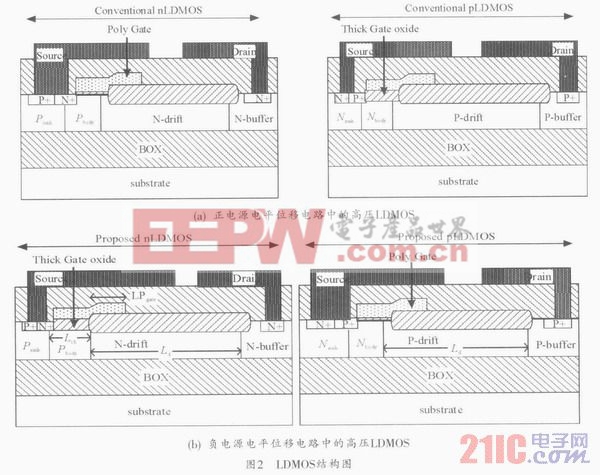

由于负电源供电的电平位移电路结构的改变,应用于正电源的常规nLDMOS和pLDMOS不能满足该电路结构要求。在正电源供电的电平位移电路中,由于pLDMOS的源端接高压电源,其栅源需要承受高压,所以pLDMOS采用了厚栅氧的结构,如图2(a)所示。在使用负电源的电平位移电路结构中(图1(b)),pLDMOS的源端为逻辑高压8V,栅端由低压逻辑0~8V电压控制,因此栅源不再承受高压。但是nLDMOS的源端为负电源的最低电位,其栅源需要承受高压,因此高压nLDMOS需要采用厚栅氧结构,如图2(b)所示。本文引用地址:https://www.eepw.com.cn/article/178713.htm

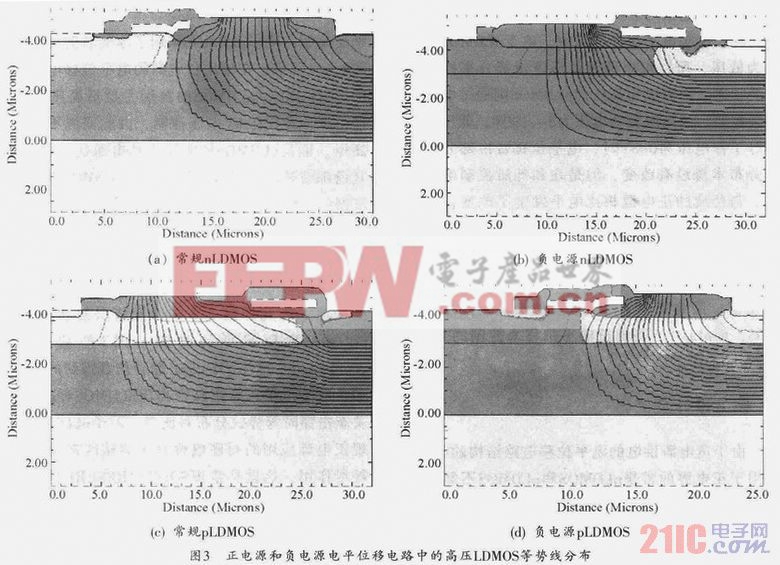

电源的改变不仅仅改变了电路的结构,nLDMOS的厚栅氧,同时器件的耐压机理也发生了改变。考虑到低压管的背栅效应,SOI材料的衬底只能接地,因此源漏电平的改变将引起nLDMOS和pLDMOS耐压机理的改变。图3是利用工艺(Tsuprem4)、器件(Medici)联合仿真得到的正电源和负电源电平位移电路中高压nLDMOS和pLDMOS关态击穿时等势线分布对比图。对于nLDMOS,常规正电源应用的衬底电位对于漂移区来说是辅助耗尽作用,这就是常规SOI中的RESURF原理。但是对于负电源的nLDMOS来说,衬底不再起辅助耗尽SOI层漂移区的作用(图3(b))。对于pLDMOS来说,情况刚好相反。所以针对负电源应用,两种器件都要进行相应的优化处理。

DIY机械键盘相关社区:机械键盘DIY

评论