时间交替超高速ADC技术解析

输出采集时钟(DCLK)也被分离,可在SDR或DDR模式中配置。但是,多路分离带来新的考量问题,因为现在增加了输入采样时钟和各模数转换器DCLK输出之间的协调不确定性。为了克服这个问题,ADC083000可以精确复位采样时钟输入与DCLK输出的关系,这由用户提供的DCLK_RST脉冲确定。这允许一个系统中采用多个模数转换器,使其DCLK(和数据)输出在与采样共享输入时钟相同的时间点跃迁,从而实现多个模数转换器之间的同步。

数字交替方法

模拟校准是实现高动态范围、高整体集成解决方案的行之有效的方法,其集成的时钟相位、增益和偏移调整功能可提供高精确度。

模拟校准的可行替代方法是用于交替数据的数字校正算法。此方法寻求在数字域校正数据转换器失配,而不需要任何模拟偏移、增益或相位校正。理论上,这些算法可独立工作,不需要实现校准或了解输入信号。此外,数字偏移、增益和相位校正因素的汇合时间也是关键系统指标。

SP Devices公司开发的算法经过验证是符合这些条件的一种数字后处理方法。SP Devices的ADX技术持续提供模数转换器的增益、偏移和时间偏差误差的后台估计值,而不需要任何特殊校准信号或后期微调。此算法对于校正静态和动态失配误差很有效。

ADX技术估计误差,并使用抑制的全部失配误差重新构建信号。IP-core的误差校正算法对于任何输入信号类型均有效。该数字信号处理的结果超出ADX核心的时间交替频谱,并消除了与失配相关的明显交替失真杂散信号。

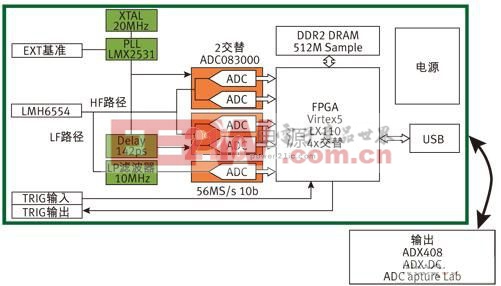

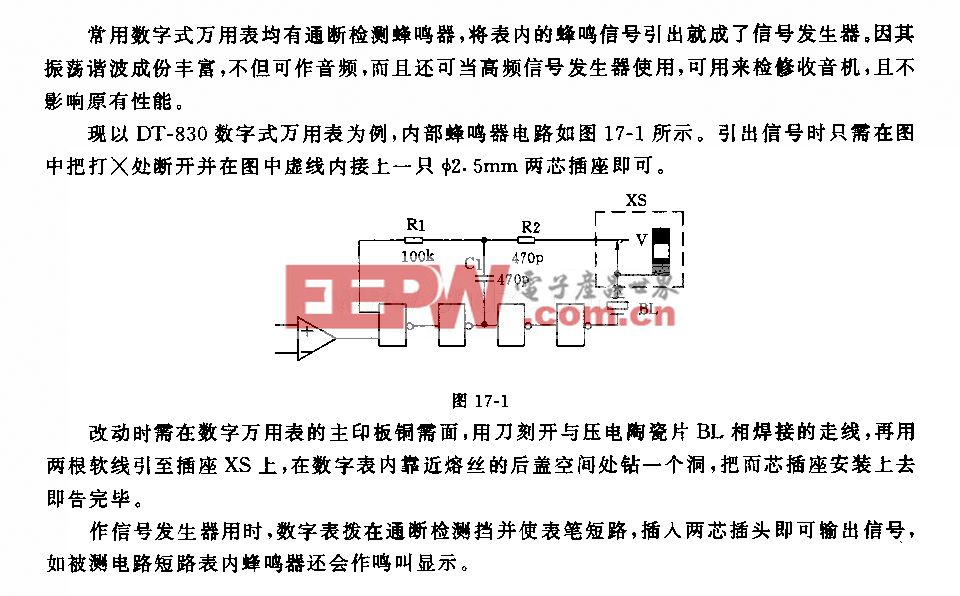

配备两个ADC0830003GSPS、8位模数转换器的美国国家半导体参考板展示了SP Devices的算法。数据转换器使用板上FPGA中内嵌的ADX技术实现交替。图3为7GSPS数字化卡的框图。

图3:含LMX2531和LMH6554的ADQ108系统框图。

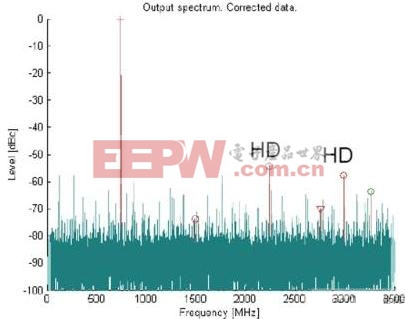

图4是SPDevicesADQ108数据采集卡的输出频谱性能图。值得注意的是杂散峰值部分是由于谐波失真所致,交替杂散信号已大幅减少。关于数据采集卡的其他详细信息,请参见:http://spdevices.com/index.php/adq108。

图4:采用ADX技术的模数转换器组合频谱。

超高速模数转换器支持电路

为了实现使用ADC083000等数据转换器可达到的高级性能,需要确保支持电路具有与数据转换器本身相匹配的性能。支持电路的关键要素包括:

1) 高性能、低抖动时钟源。

2) 用于驱动模数转换器输入的高线性、低噪声放大器或平衡/不平衡变换器。

建议使用LMX2531或LMX2541时钟同步器生成低抖动模数转换器时钟信号,使用LMH6554驱动模数转换器模拟输入。

LMX2531集成了锁相环(PLL)和VCO,并提供优于-160dBc/Hz的噪声底。可提供多种版本芯片接纳553MHz至2790MHz的不同频带。

为了实现更好的高输入频率SNR性能,建议使用较低相位噪声LMX2541作为适合的时钟源。LMX2541在2.1GHz具有小于2毫弧度角(mrad)均方根的噪声,在3.5GHz具有小于3.5mrad均方根的噪声。LMX2541的锁相环具有-225dBc/Hz的校正噪声底,能在整数和分数模式中以最高104MHz相位检测速率(比较频率)工作。

LMH6554是业界最高性能的差分放大器。LMH6554的低阻抗差分输出可用于驱动模数转换器输入和任何中间滤波级。这种宽频全差分放大器可驱动8位至16位高速模数转换器,在800MHz以下具有0.1dB增益平坦度,在250MH时具有72dBcSFDR,并具有0.9nV/sqrtHz低输入电压噪声性能。

LMH6554在75MHz以下具有16位线性度,可驱动2V峰-峰电压至最低200Ω负荷。LMH6554通过外部增益设置电阻器和集成共模反馈,可使用差分-差分或单端-差分配置。放大器提供最高1.8GHz的大信号带宽,8dB噪声和6,200V/μs转换速率。

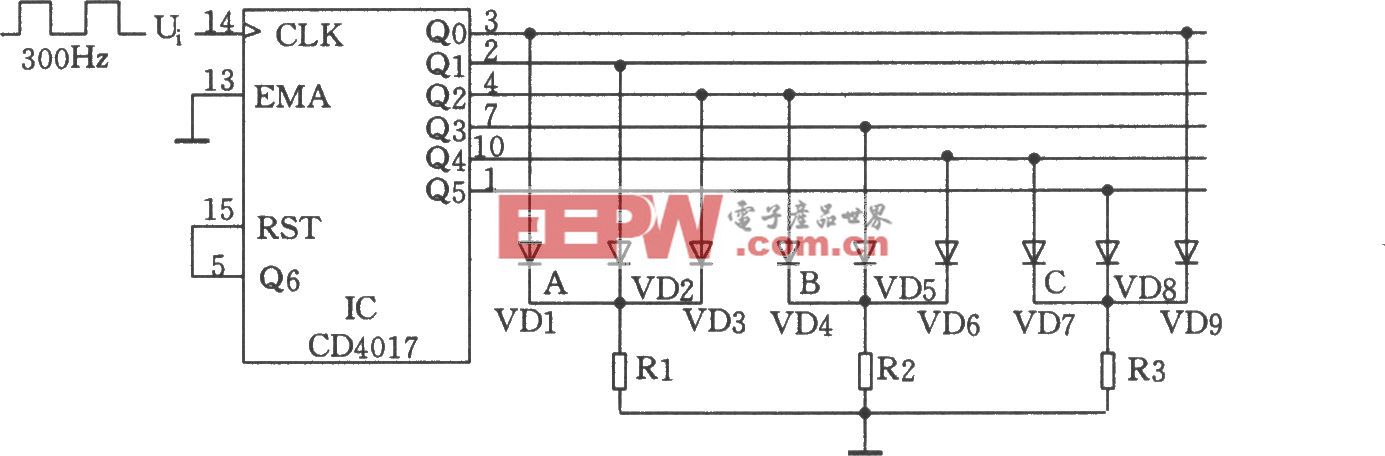

图5显示使用上述支持元件的典型应用框图。

图5:典型系统框图。

本文小结

本文阐述了交替高速模数转换器的难点和解决这些问题的几种方法。由于交替技术、低抖动时钟源和高性能放大器的进步,现在可以实现保持超过6GSPS的优异动态性能。

评论