LMK0480X 产品供电电源设计指导

• VCC2, VCC3, VCC10, VCC11, VCC12, VCC13 是给芯片的 12 路输出提供电源(一个供电管脚负责两路输出)。如果其中几路输出相同的频点时,这几路的供电可以连接到一起,共享供电支路,简化设计。由于输出频率都比较高,所以对于这几路供电管脚建议增加磁珠,以降低芯片开关噪声对于芯片整体供电的影响,同时提高通道间的隔离。同时如前面提到,由于芯片内部已经集成了高频去耦电容,所以不需要外部的去耦电容。

当输出的频率较低时(〈10MHz),或者输出单端 LVCMOS 或者高摆幅的 LVPECL 信号时,为了降低供电环路的阻抗,建议去掉磁珠或在管脚处增加一个大一点的去耦电容,提供开关电流。

• 当输出时钟类型是 LVPECL 时,应防止输出到地有电容。因为这样很容易形成到地的短路环路,不仅需要电源管脚提供很大的开关电流,同时将频率噪声引入到地平面,给系统带来了干扰。

2.2 PSRR(Power Supplier Rejection Ratio)性能分析

为了表征各类不同供电管脚的电源噪声对 LMK0480X 输出噪声的影响,通常采用电源噪声抑制比 PSRR来表征锁相环芯片的抗电源噪声能力,本节通过实际测试样例评估 LMK0480X 的供电噪声抑制性能。

2.2.1 测试设置

PSRR 测试基于 LMK0480X 评估板,在这些测试中,测试框图如 Figure2,设置如下:

1. 外部 VCXO 使用独立的干净电源供电,排除 VCXO 对测试结果的影响。

2. 去掉芯片外部的去耦电容和磁珠,排除这些器件对芯片 PSRR 的影响。

3. 干扰源通过信号发生器产生合路进入测试的电源管脚。干扰源的频率从 50KHz 到 2 MHz 连续扫描,测试干扰信号在环路带宽内外,对于芯片 PSRR 性能的不同影响。

4. 干扰源输入信号的摆幅固定在 Vin = 100mV;测量输出端口载波两侧的对应的干扰源带来的杂散(偏移对应的干扰源频率)的功率 Ps dBm,将 Ps 转换为电压幅度 Vs,转换公式以及 PSRR计算公式如 Equation 1 。

2.2.2 不同供电管脚噪声对 LMK0480X 输出噪声的影响分析

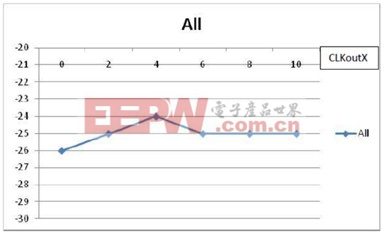

1.当干扰电源输入到所有的供电管脚,测试所有输出管脚的 PSRR。如下图所示,几乎所有输出端口的 PSRR 大约是 25dBc。

Figure 3 干扰电源应用到所有供电管脚的 PSRR 测试结果

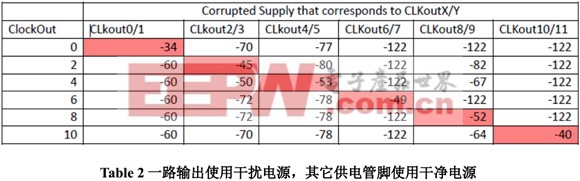

2.只将干扰源输入到 LMK0480X 其中一路输出管脚供电,其它供电管脚都使用干净的电源,PSRR 测试结果如下图;可以看到,只有使用干扰电源的那一路 PSRR 结果比较差,其它输出受到干扰电源的影响不大,都可以达到 60dBc 以上。

在没有使用干扰电源的端口加上去耦电容,继续上面的实验发现,可以发现受到电源干扰的输出端口的 PSRR 也略有改善,但仍然是最差。

评论