法拉电容在RAM数据保护中的应用

(1) 主控制程序

上电进行必要的CPU初始化后,检查正常掉电标志和RAM Check Sum计算检查,以确认RAM中数据是否正常。如果正常,就进行掉电前的现场恢复。其主程序流程框图如图2所示。

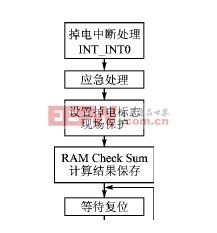

(2) 掉电中断处理程序

CPU收到掉电信号(PW_DN)中断时,CPU进行掉电应急处理和保护现场,设置正常掉电标志,保存RAM Check Sum计算结果,以备上电时检查RAM数据是否被破坏。其流程框图如图3所示。

图3 掉电中断处理流程

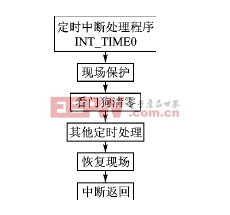

图4 定时中断处理流程

(3) 定时中断处理程序

看门狗定时器电路需要在每1.6 s内清零,在定时中断处理程序中调用看门狗清零子程序。定时中断时间要设在1.6 s以内,例如100 ms。定时中断处理流程框图如图4所示。

结语

在本应用实例中,经测试,掉电后RAM数据后备时间是10~14天,且数据可靠,系统运行稳定。显然,选择更大容值的法拉电容将有更长的后备时间。在控制系统的产品设计中,为提高产品的可靠性、降低成本、增强产品在市场上的竞争力,本文提供的方案具有参考价值。

超级电容器相关文章:超级电容器原理

评论