基于FPGA动态背光源及其驱动电路设计

3 软件设计

本款芯片的控制信号由Altera 公司的型号为EP1C3T144C8 的开发板供给,晶振为50MHz。

从实验得到的效果来看,该款芯片的数据传输机理为:每个传输周期,每遇SCLK 上升沿将会从SIN 口读入1bit 数据存入寄存器,在SCLK 下降沿时,将读入的数据从SOUT 传出(内部对数据仍有保留) 输给下一级,直至读入288bits 数据。每12bits 为一组,分别送到各自的通道,并且每组数据先读入的居于较高位,然后依次排列。例如,读取的数据按时间先后排列为1、0、0、0、0、0、0、0、0、0、0、0,则相应的控制信号为100000000000,那么控制通道的占空比即为:

根据PWM 调制面积相等的原则,有效电压约为提供电压的一半。

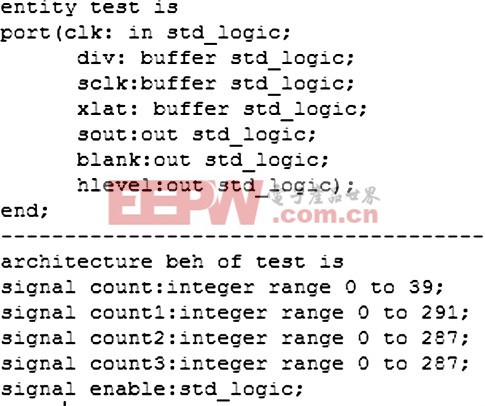

按照仿真条件的要求,SCLK 时钟信号需要在每接收完288bits 时有段时间的低电平,尽量满足芯片的时序要求。另外,控制信号BLANK 在每个周期空闲时(不传输数据时),需要有个高电平变换,这样可以将锁存器里面的数据清零,以便接受新一轮的控制数据,否则,灯的亮度明显会偏暗。

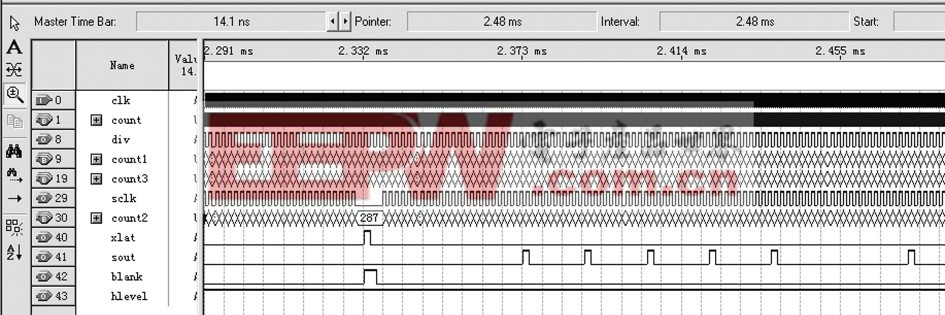

RGB 数据经过FPGA 的处理,转换为相应的灰度值,然后再计算出相应的控光参数Ki (我们可以分的灰度级别不超过4,096),传输给TLC5947的SIN,即可以实现动态背光调节。

图4 输入输出信号设置

图5 信号仿真图

图6 PWM 调制输出波形

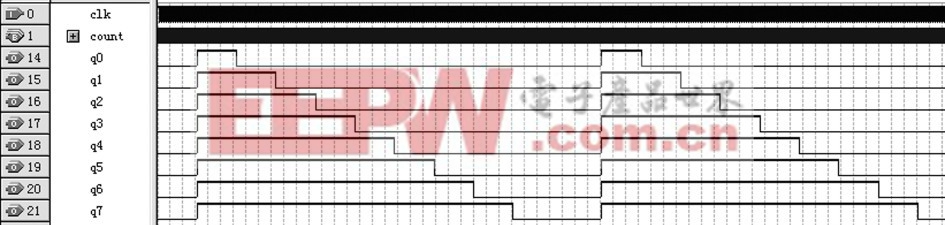

4 结论

通过理论分析和实验测试,动态背光调节控制系统在节能和提高图像显示对比度等方面做得都较好,这在重视节能减排、建设和谐社会的今天以及对LCD 显示器的未来发展都具有很好的应用前景。

图7 即通过FPGA 控制以及基于图像像素控制得到的动态背光调节效果图,从中可以看到,如果在以前LCD 静态背光的条件下,则所有背光LED 灯的亮度将会和最亮的(右下角)一致,而现在我们将之分割为各个不同区域,使得每个区域均有自己的最佳亮度,而不必以整个图像最亮一点为标准,并且不影响显示效果。这样,也就实现了我们预期的动态调节的目的。

图7 背光源效果图

评论