基于PCIe总线的航空视频采集记录系统的设计

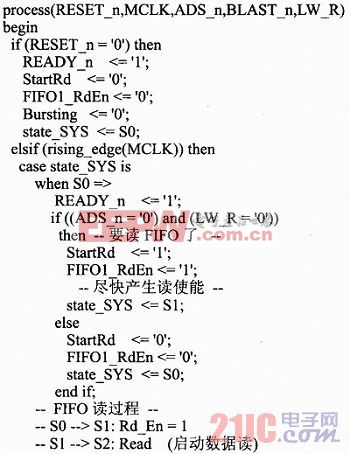

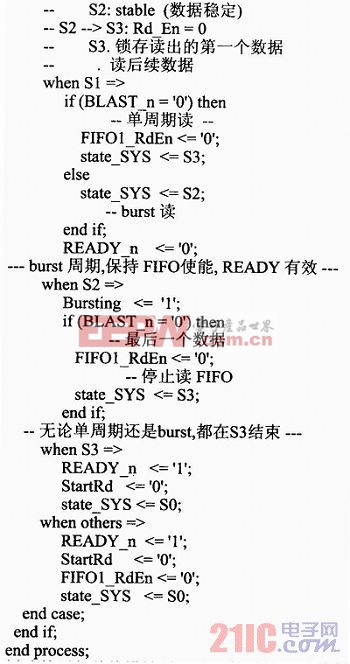

PCIe桥接口的逻辑设计最重要的部分是为它的局部总线(Local bus)提供无缝的粘合逻辑,支持PCIe的单次访问和burst访问。其接口状态机如下:

桥片的局部总线设计了50MHz的时钟,对32-bit数据宽度,理论上可以达到200Mb/s的吞吐率。经过应用软件的实测,可以达到143Mb/s的速率,考虑到软件的许多开销,这个速率已经比较理想了。

5 系统的软件设计

系统的软件设计平台采用WindowsXP Embedded,软件分为针对本硬件系统的驱动程序和视频压缩与处理的应用程序。应用程序把视频存为普通播放器能播放的视频格式,每帧视频为256行×256列共64K像素。在驱动软件中,当打开设备时,申请一组缓冲,共128个缓冲。这个缓冲对应用程序是透明的,每个缓冲可以存放一个完整的视频帧,如图6所示。驱动程序中有两个主要线程,中断线程和数据读出线程。

在逻辑设计时,每当FIFO中写入4kx32bi时产生中断,则驱动程序的中断线程在响应中断时,每次至少读16kB。在中断响应读取FIFO数据时,不要用类似于for(;;)的软件循环实现,这种策略在硬件时序上属于单次访问,效率低下。只有DMA才能触发逻辑设计中的burst周期,最大限度利用硬件性能。在启动DMA时,一定要使能它的burst位操作长度固定为16kB。这样,每次中断响应就变成了维护DMA当前写入缓冲的指针,填入当前写入缓冲地址,然后启动DMA。本文引用地址:https://www.eepw.com.cn/article/165890.htm

在应用程序中,使用一个定时线程,通过驱动程序读取视频数据,然后经过压缩,存放成JPEG2000格式的视频文件。定时读取视频数据的算法需要进行优化,因为如果数据读出线程太慢,中断线程写入时可能覆盖未读走的缓冲,会造成存储视频出现丢失数据帧的现象,影响记录视频的连续性。

5 结束语

本文采用FPGA与嵌入式CPU大容量数据存储相结合的方案,在系统各个处理环节均充分考虑到对视频数据采集记录实时性和可靠性的要求,设计了机载多通道实时视频数据采集记录系统。系统硬件设计简单,并且可同时采集多路视频数据。在某型数字化对抗训练评估系统中的应用表明,本设计方案满足了预期的指标要求,解决了载机任务系统多路视频数据采集与实时记录的关键问题,在实时视频信息采集和数据记录应用中具有较好的通用性和扩展性。

评论