基于PCIe总线的航空视频采集记录系统的设计

3 系统的逻辑设计

在硬件设计的基础上,逻辑设计成为整个系统性能实现的关键。逻辑设计完成整个系统的时序控制、视频数据流的采集与解码、视频回放的编码和PCIe桥接口的设计。

3.1 视频解码

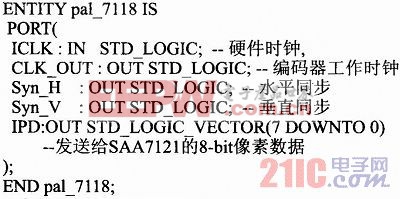

在逻辑设计中,视频解码的功能是将DS90LV032所转换的单端信号解码后写入FIFO缓冲,由后续逻辑读取处理。其逻辑接口的VHDL形式描述如下:

上层逻辑调用此模块,每调用一次,配置一个寄存器。所有128个寄存器的配置数据是预先定制的,存放在常量数组中。

经过初始化后的SAA7121可以正常工作了。此时逻辑应该不断输送视频数据。其逻辑接口可以描述如下:

3.3 PCIe桥接口设计

数据高速传输主要体现在PCIe总线的实际吞吐量,此为解码后的数据传输的瓶颈。逻辑设计要特别考虑到软件的方便和高效。接口逻辑设计集中在中断逻辑和数据传输的burst方式上。

需要传输的视频数据,首先送入一个FIFO,写入端为32k×16bit,读出端为16k×32bit,写入时既适合了视频数据的宽度,读出传输时又发挥了PCI32-bit总线的优势,加快了转换。中断逻辑设计如下:

(1)当写入数据达到FIFO容量的1/4时,即写够4k×32bit时产生中断。这个条件可根据FIFO的可编程空判断,亦即PRG1 Empty=‘0’时产生中断。

(2)当主机响应中断,开始读FIFO数据时撤销中断。

(3) 当本次burst读结束后,才允许根据条件重新判断中断条件。

评论