基于PI控制的全数字锁相环设计

2 全数字锁相环的设计和软件仿真

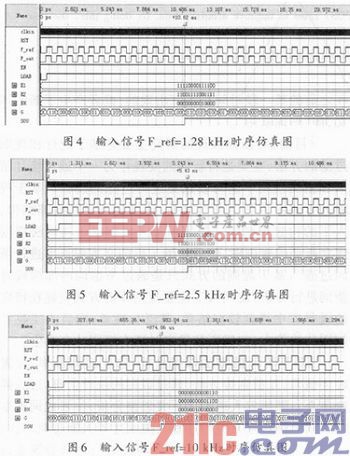

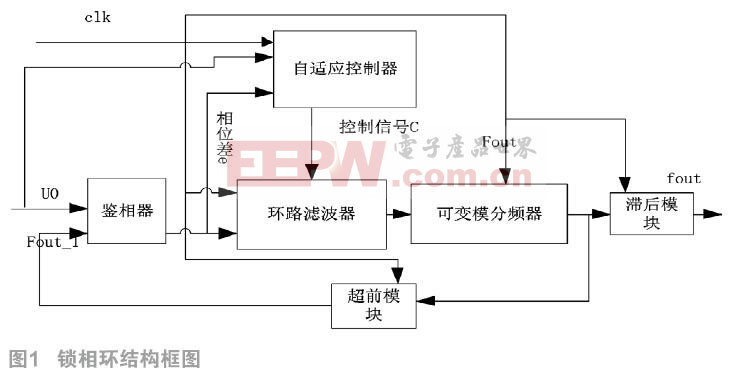

依据图1锁相环系统的结构,利用Altera公司的QuartusⅡ设计软件,采用自顶向下的模块化设计方法,用VHDL对全数字锁相环的各个部件分别进行编程设计,然后对该系统做综合设计和仿真。最后,采用Altera公司的Cyclone系列的FPGA器件实现了锁相环系统的硬件功能。图3为QuartusⅡ软件设计的基于PI控制的二阶全数字锁相环的电路原理图。此锁相环电路原理图由D触发器、双D触发器鉴相器(FPD)、数字环路滤波器(DLF)、数控振荡器(DCO)和锁定检测模块组成。D触发器起到延时作用,使得输入信号与DCO的输出信号同步。FPD的作用是比较输入与输出矩形信号的前沿,并产生超前/滞后的标志信号和频率/相位误差序列。DLF中的周期性归零可逆计数器和不归零可逆计数器根据频率/相位误差序列生成比例积分控制信号,即DCO的低位控制字。DCO可根据高位控制字和低位控制字的变化自动调节其输出信号的频率。锁定检测模块根据频率/相位误差来判定系统是否已经锁定,并发出相应的锁定标志信号。本锁相环系统的设计参数如下:DLF内周期性归零可逆计数器和不归零可逆计数器的位长为14位;DCO中累加器的位长为28位,系统高速时钟频率clkin为1.25 MHz,比例积分控制码组G的字长为14位,自由振荡频率f0控制码组C的字长为14位。图4为输入信号F_ref=1.28 kHz的时序仿真图,锁频时间T=10.62 ms。图5为输入信号F_ref= 2.5 kHz的时序仿真图,锁频时间T=5.43 ms。本文引用地址:https://www.eepw.com.cn/article/159407.htm

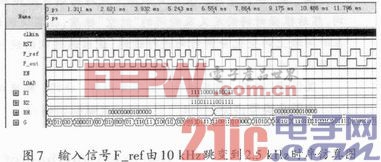

图6为输入信号F_ref=10 kHz的时序仿真图,锁频时间T=874.86 μs;图7为输入信号F_ref由10 kHz跳变到2.5 kHz时的时序仿真图;图中clkin为系统时钟,RST为系统复位信号,F_ref为输入信号,F_out为输出信号,EN为使能计数控制信号,LOAD为置数控制信号,BH为数控振荡器高位控制字,G为数控振荡器低位控制字,K1,K2为数字环路滤波器的预置数。通过对所设计的全数字锁相环的时序仿真图可以看出:适当地调节参数BH,K1和K2,锁相环能够锁定不同频率的输入信号。而且,该系统具有一定的自适应的特性,对频率发生跳变的输入信号也能够实现快速跟踪。

3 结语

实验表明:该锁相环在一定的频率范围内能较快的锁定输入信号,在15个输入信号周期内环路就进入锁定状态,相位抖动小于输出信号周期的5%。该全数字锁相环具有电路结构简单,锁定速度快,易于集成等特点。可采用VHDL语言完成系统设计,使用EDA软件进行综合仿真,并可制成片内锁相环。

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理 锁相放大器相关文章:锁相放大器原理

评论