一种基于频率预测算法的快速锁定全数字锁相环

谭宁禹 (大连理工大学 微电子学院,辽宁 大连 116024)

摘 要:近年来,5G和物联网应用对片上系统时钟提出了新的需求。锁相环在片内发挥着重要的作用,以产 生不同的时钟源。这些新需求的主要关注点快速锁定、低功耗、低噪声和小面积。随着CMOS工艺的发展,模 拟锁相环的工作电压逐渐降低,其设计面临着巨大的挑战。根据市场需求,采用全数字锁相环(ADPLL)进行数 字设计,以减少设计时间和设计工作量。此外,使用标准单元实现的ADPLL不仅可以加快设计时间,而且可以 提高可移植性。当系统处于休眠状态时,锁相环功耗控制着系统的待机功耗。因此,如果锁相环可以快速锁定 频率和相位,锁相时间就可以减少,这样锁相环就可以在低功率模式下关闭。本文提出了一种基于频率预测算 法的快速锁定ADPLL。该锁相环在中芯国际 130 nm CMOS工艺中进行了实现和验证。

0 引言

近年来,随着5G和物联网的发展,锁相环(PLL)在 片上系统(SoC)中扮演着重要的角色。在一个SoC中, 通常需要几个锁相环为不同的I/O接口提供不同的时钟 源。锁相环产生不同的频率,适用于不同的应用场合, 广泛应用于移动通信系统、无线通信系统和生物医学电 子领域。传统锁相环是由电荷泵锁相环实现的,在先进 的CMOS工艺中,锁相环的设计面临泄漏电流的挑战。 此外,电压控制振荡器(Kvco)的增益由于控制电压范围 的缩小而增大。因此,它很容易遭受噪声对控制电压的 影响。传统锁相环中含有一些无源器件,模拟环路滤波 器芯片面积大、成本高。并且传统锁相环锁相时间长, 功耗高。因此,随着工艺尺度的减小,由VCO、电荷泵 和模拟环路滤波器组成的锁相环不适合新的要求,即低 功耗、低电压、低芯片面积,尤其是快速锁定。

全数字锁相环(ADPLL)利用了CMOS工艺的优 点[1],与传统锁相环相比,ADPLL采用数字电路代替无 源器件。将VCO转换为数字控制振荡器(DCO),并将模 拟滤波器转换为数字滤波器。芯片尺寸减小,芯片成本 相应降低。因此,ADPLL可以在低电压下工作,芯片 面积小。

为了实现快速锁定,需要对全数字锁相环引入快速 锁定算法。这里采用了一种新颖的频率预测算法来对数 控振荡器控制字进行预测,来加快锁定速度。

1 快速锁定全数字锁相环

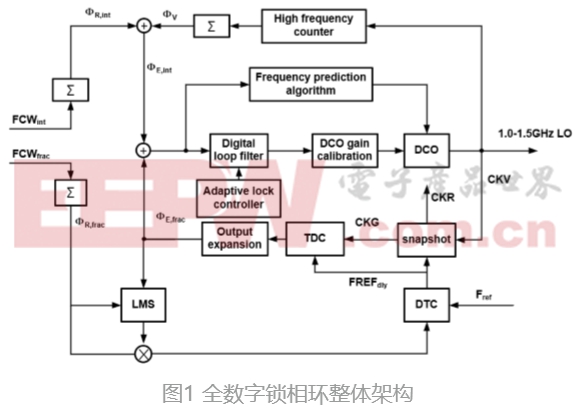

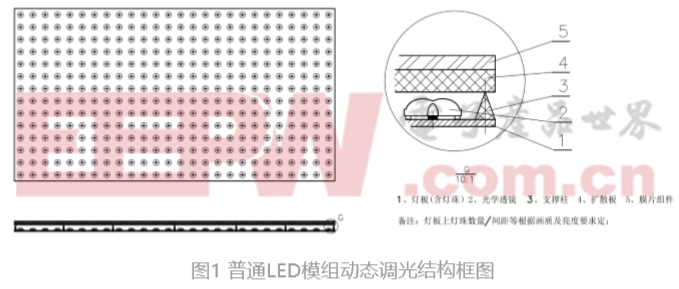

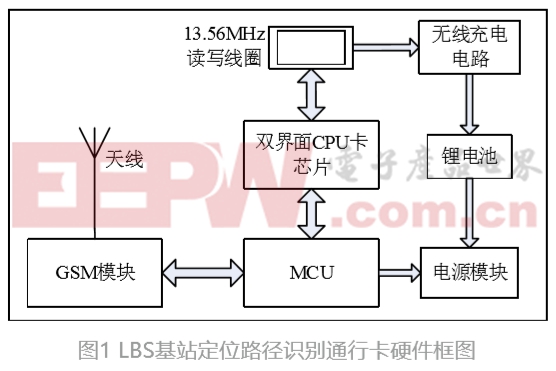

1.1 全数字锁相环架构 采用基于计数器的全数字锁相环系统结构[2],本论 文提出了一种宽频带的,低功耗的、能够实现自适应快 速锁定的全数字锁相环系统架构,如图1所示。其中,模拟电路包括数字时间转换器、时间数字转换器、LC 数控振荡器。高速数字电路包含有snapshot电路、可变 时钟相位累加器、Σ-Δ调制器。而低速数字电路则包含 有限状态机、数字滤波器、相位检测器、DTC增益校正 电路、TDC输出扩展电路、DCO增益校正电路、DCO 细调bank行列控制逻辑、DTC输入温度码解码电路[3]。

首先,整数输入分频比和输出时钟分别累加得到整 数相位与可变相位。之后,这两个相位被送到相位检测 器中进行做差,得到整数相位差。同时,参考时钟通过 数字时间转换器进行延迟,得到。采用一个快照电路提 供重定时时钟CKR和门控时钟CKG,利用时间数字转换 器检测CKG和之间的分数相位差。随后,整体的相位差 通过将和 相加得到。最后,一个数字滤波器将处理得 到数控振荡器控制字来控制数控振荡器的振荡频率。

1.2 频率预测算法

快速锁定算法在原理上包含两种类型。第一个是在 环路开始运行之前预测数控振荡器控制字。该方法减 小了初始相位差。另一种是采用换档算法自适应控制 带宽。既满足锁定速度的要求,又满足相位噪声的要 求[4]。

由于我们为了获得较好的相位噪声,选择了LC振 荡器,而不是环形振荡器,LC振荡器的调谐曲线并不 是严格线性的,所以与环形振荡器相比其频率预测无法 直接精确得到控制字的值,但是由于粗调和中调阵列的 调谐步长较大,所以仍然可以得到较为精确的预测值。

在锁定过程中,DCO输出周期可以看做是粗调控制字和中调控制字的函数,对于采用线性度极高的由相同 的延时单元级联组成的环形振荡器来说,该函数关系可 以看成是严格线性的,所以,直接采用基于线性关系的 频率估计算法进行一次线性插值即可以实现快速锁定。 但是对于LC振荡器,输出频率 ,一方面受限于工艺库,片上电感的值在整个输出频率范围内会有 1 nH左右的波动,另一方面,电容值随着控制字是线性 变化的,所以输出频率f随着控制字的变化是斜率递增 的,输出周期随着控制字的变化是斜率递减的,因此输 出周期与控制字并不是严格线性的。为了在覆盖较大的 频率调谐范围的同时,实现较为精细的频率分辨率, DCO的调谐阵列采用了三级调节的方式,粗调阵列调谐 步长26 MHz/LSB,中调阵列2.5 MHz/LSB,细调阵列 60 kHz/LSB,其中粗调和中调阵列采用了type I环路控 制,相对于传统的type II环路可以加快锁定速度,而细 调阵列采用type II环路控制,有利于压制相位噪声,实 现最终的锁定。所以,可以针对粗调控制字利用线性插 值法进行频率预测,进一步加快锁定速度。

,一方面受限于工艺库,片上电感的值在整个输出频率范围内会有 1 nH左右的波动,另一方面,电容值随着控制字是线性 变化的,所以输出频率f随着控制字的变化是斜率递增 的,输出周期随着控制字的变化是斜率递减的,因此输 出周期与控制字并不是严格线性的。为了在覆盖较大的 频率调谐范围的同时,实现较为精细的频率分辨率, DCO的调谐阵列采用了三级调节的方式,粗调阵列调谐 步长26 MHz/LSB,中调阵列2.5 MHz/LSB,细调阵列 60 kHz/LSB,其中粗调和中调阵列采用了type I环路控 制,相对于传统的type II环路可以加快锁定速度,而细 调阵列采用type II环路控制,有利于压制相位噪声,实 现最终的锁定。所以,可以针对粗调控制字利用线性插 值法进行频率预测,进一步加快锁定速度。

线性插值的原理如下,输入时钟周期Pref 和输出时 钟周期Pckv的比例R是粗调控制字和中调控制字的函数:

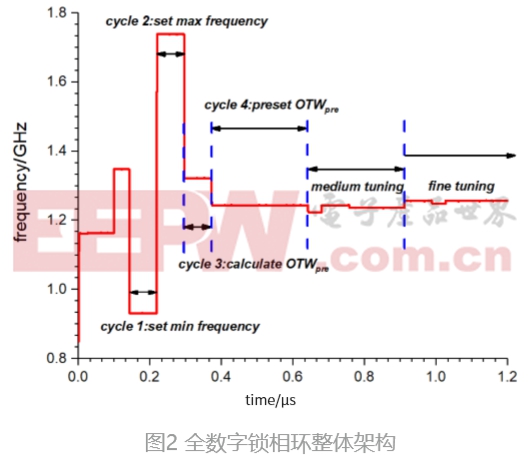

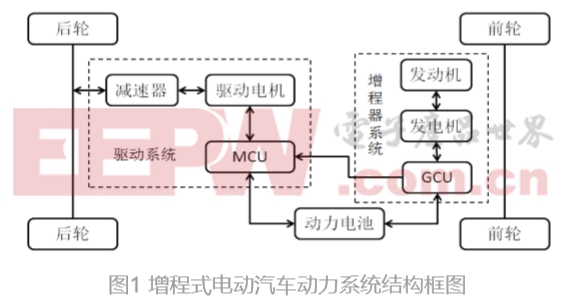

针对实际中的LC振荡器,R随着粗调控制字和中调 控制字的增加而减小,但并不是严格的线性变化,可以 采用线性插值进行拟合。目标是找到使得周期比最接 近理想整数分频比FCW时的粗调谐字[5]。在系统重置之 后,有限状态机首先控制系统进入频率预测状态。整个 频率预测过程需要四个时钟周期来完成,如图2所示。

第1个周期设置控制字OTWmax=31,控制DCO震荡 在最高频率,通过计数器测得此时的R的最大值:

第2个周期设置控制字OTWmin=0,控制DCO震荡在 最低频率,通过计数器测得此时的R的最小值:

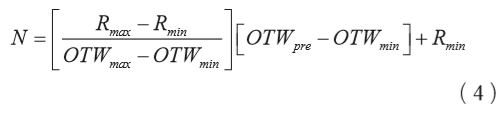

第3个周期利用线性插值法,设定线性插值的区间 为(R min,Rmax),根据线性插值公式:

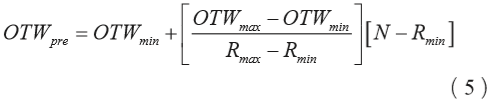

得到线性插值预测值:

第4个周期利用该线性插值预测值对粗调阵列进行 预置数,可以缩小初始状态的相位差,缩短锁定时间。

2 仿真结果

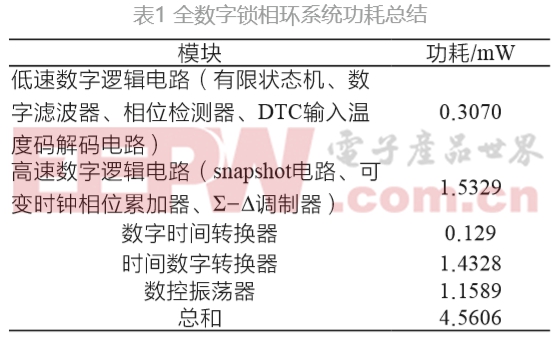

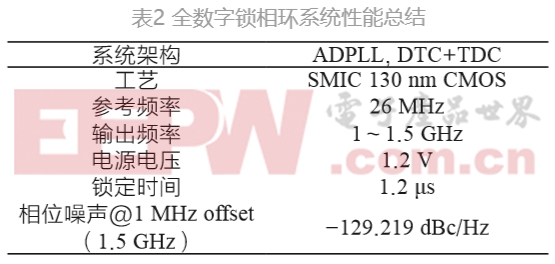

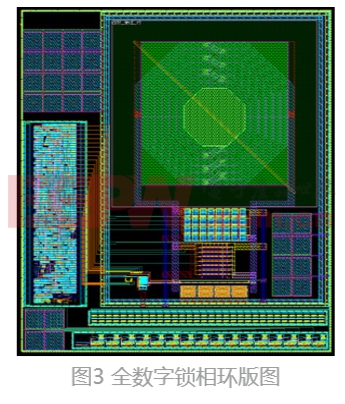

本ADPLL在中芯国际130 nm CMOS工艺中实现。 系统功耗总结如下表1。系统性能总结如表2所示。系统 版图如图3所示。

3 总结

本文提出了一种新的快速锁定全数字锁相环,该 ADPLL具有功耗低、面积小、噪声低、锁相速度快等 优点。引入的频率预测算法可以在环路锁定开始前完成 数控振荡器控制字的预测,从而极大减小上电和跳频时 的锁定时间,满足快速锁定的需求。

参考文献:

[1] LIU Y H, HEUVEL VAN DEN J H C, KURAMOCHI T, et al. An Ultra-Low Power 1.7-2.7 GHz Fractional-N SubSampling Digital Frequency Synthesizer and Modulator for IoT Applications in 40 nm CMOS[J]. IEEE Transactions on Circuits and Systems, 2017, 64(5): 1094–1105.

[2] LIU H, TANG D, SUN Z, et al. A Sub-MW Fractional-N ADPLL With FOM of -246 dB for IoT Applications[J]. IEEE Journal of Solid-State Circuits, 2018, 53(12): 3540–3552.

[3] 应用于射频无线通信系统的多模分数分频频率综合器的设计和 研究[D]. 上海:复旦大学, 2012.

[4] CHUNG C C, LO C K. A Fast Lock-in All-Digital PhaseLocked Loop in 40-nm CMOS Technology[J]. IEICE Electronics Express, 2016, 13(17): 20160749.

[5] CHEN Y W, HONG H C. A Fast-Locking All-Digital Phase Locked Loop in 90nm CMOS for Gigascale Systems[J]. 2014 IEEE International Symposium On Circuits and Systems (ISCAS), 2014: 1134–1137.

本文来源于科技期刊《电子产品世界》2020年第03期第73页,欢迎您写论文时引用,并注明出处。

评论