功率LDM0 S中的场极板设计

由于2、4、5区中纵向电场和横向电场相比可忽略,可近似认为本文引用地址:https://www.eepw.com.cn/article/157312.htm

其他各区的对应的耗尽层厚度可由![]() 得到,而由[2]可定义

得到,而由[2]可定义

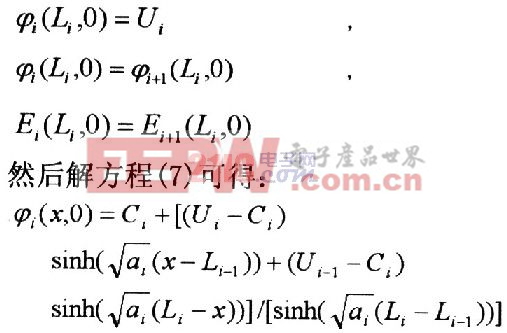

根据漂移区表面电场和电势的连续性可得出边界条件

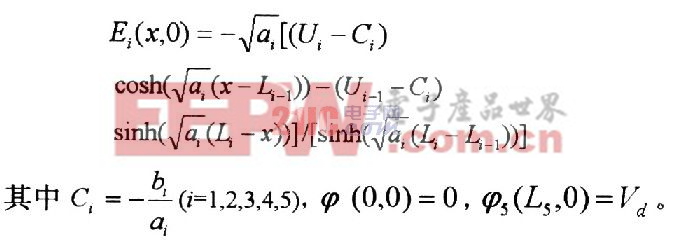

将上式在x方向微分,解得

式中Ui(i=1,2,3,4)的值可由Ei(Li,0)=Ei+1(Li,0)解得。

2 结果和分析

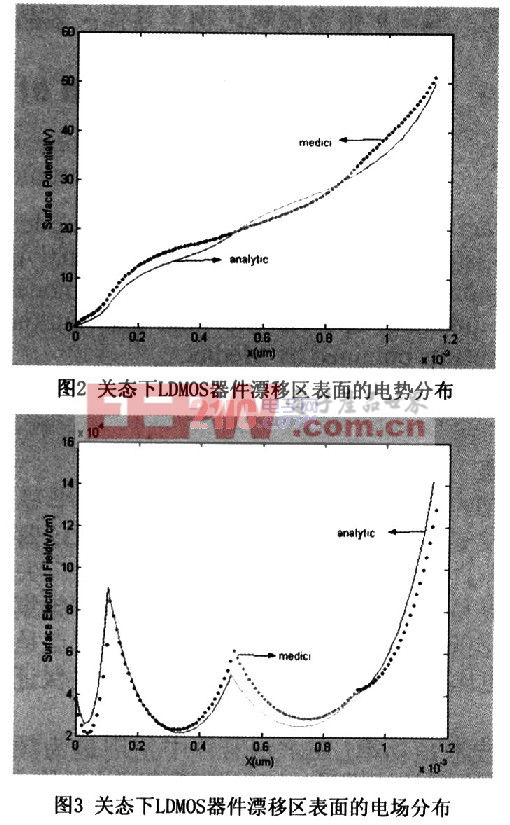

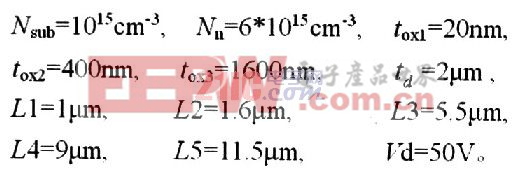

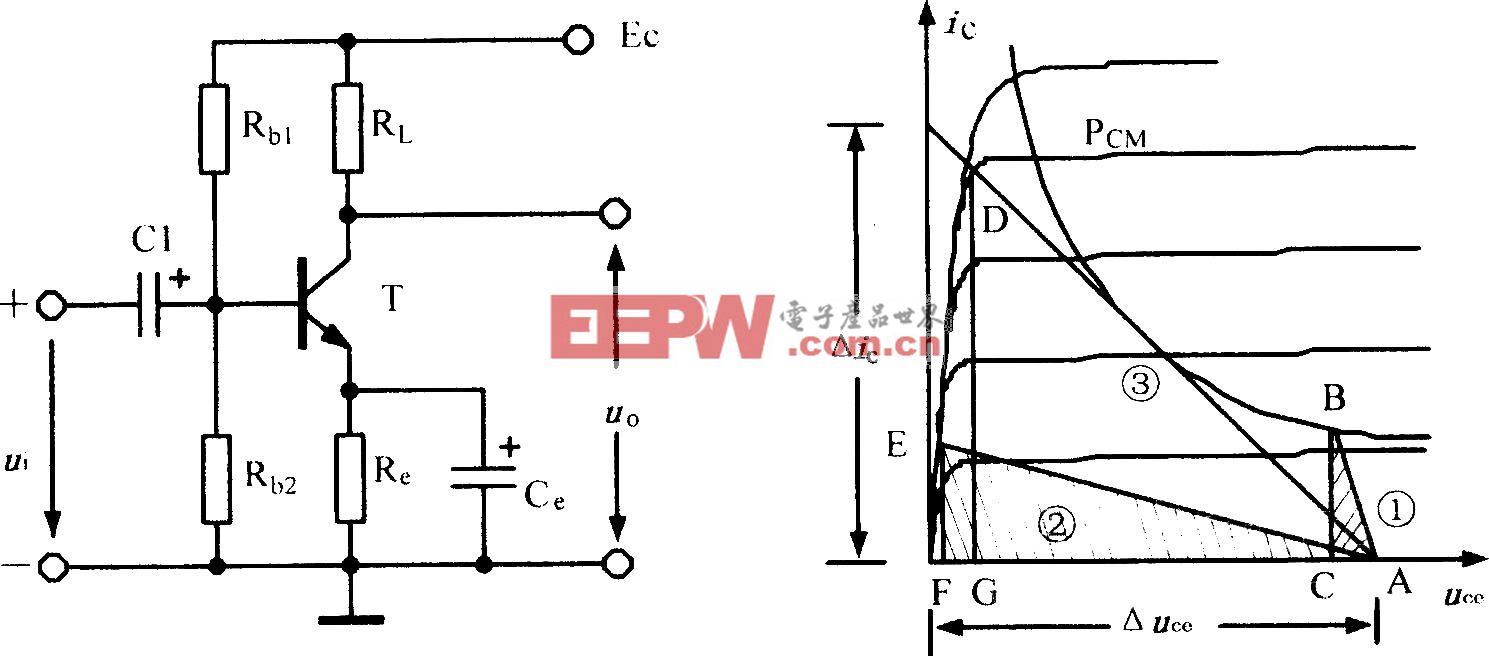

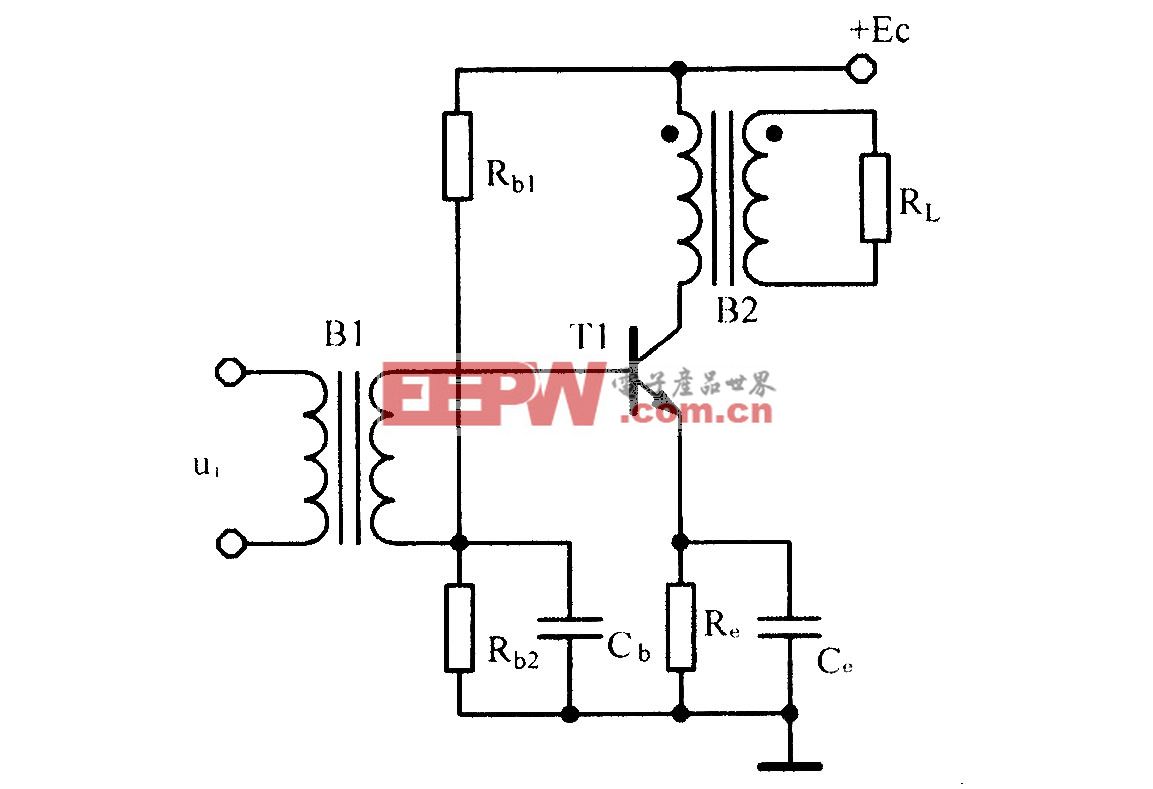

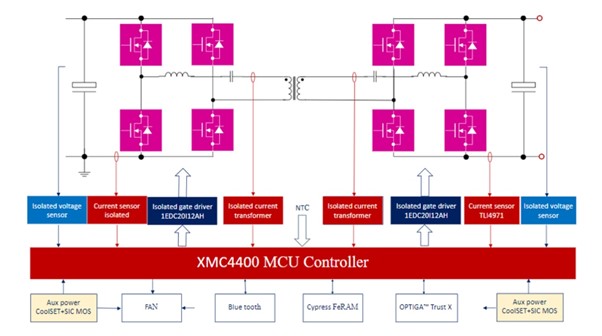

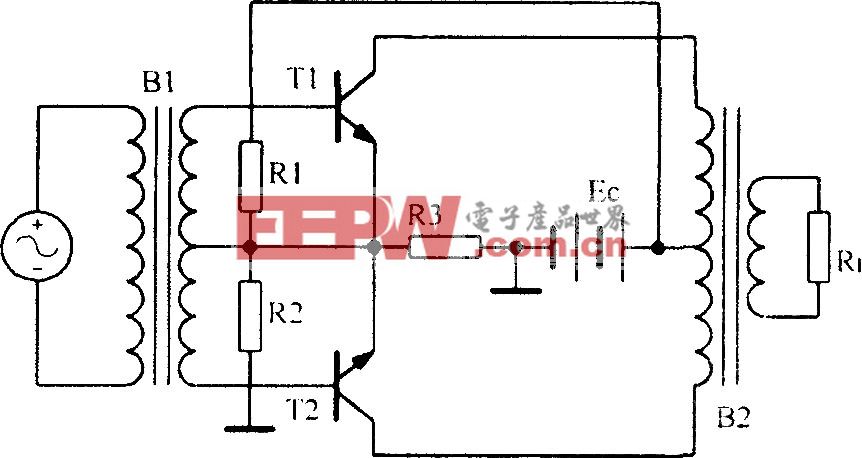

上图是在器件关态条件下漂移区表面电势和电场分布的理论值。采用的数据如下:

从图中可以看出,LDMOS处于关态时根据理论模型计算得到的结果和Medici仿真结果的比较。由于本文的模型忽略了氧化层固定电荷,所以和Medici仿真结果有差异较小。由图可见,漂移区的电场峰值出现在p阱/n-漂移区结处、场板的两端与漏端附近。这些电场峰值处也就是最可能的击穿点。

评论