高性能双通道DDS芯片AD9958及其应用

2 引脚说明

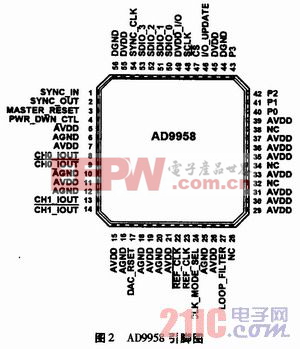

AD9958采用56脚LFCSP封装,其引脚图如图2所示,其主要引脚功能如下:

SYNC_IN:同步多片AD9958的输入信号,使用时与主器件AD9958的SYNC_OUT相连;

SYNC_OUT:同步多片AD9958的输出信号,使用时与从器件AD9958的SYNC_IN相连;

MASTER_RESET:复位引脚,高电平有效;

PWR_DWN_CTL:电源掉电控制引脚;

CH0_IOUT、CH1_IOUT:通道0、1输出端,无需上拉电阻,输出范围可达AVDD;

CH0_IOUT、CH1_IOUT:通道0、1互补输出端,无需上拉电阻,输出范围可达AVDD;

DAC_RSET:DAC复位端,为DAC创建参考电流,通过一个1.91 kΩ的电阻接至AGND端;

REF_CLK、REF_CLK:参考时钟或晶振输入端;

CLK_MODE_SEL:振荡器模式控制引脚,为1时使能振荡器为REF_CLK源,为0时不使能;

LOOP_FILTER:与锁相环环路滤波器的零点补偿电路连接,此引脚与AVDD间串接一个0 Ω电阻和680pF电容。

P0,P1,P2,P3:调制数据引脚;

I/O_UPDATE:I/O口更新寄存器控制端,此引脚上升沿数据从串口缓冲器送入寄存器。

:片选端,低电平有效,允许多芯片共用SPI总线;

SCLK:I/O口读写时的串行数据时钟输入端,上升沿写操作,下降沿读操作;

SDIO_0:专用串行I/O口引脚;

SDIO_1,SDIO_2,SDIO_3:用作串行I/O口引脚或初始化DAC输出幅度增减量控制引脚;

SYNC_CLK:同步时钟输出引脚,为系统时钟的4分频。

3 AD9958串口特点及工作模式

AD9958的串口提高了多种配置,其SPI模式与早期的DDS产品的操作模式兼容。4个串行数据引脚(SDIO_0,SDIO_1,SDIO_2,SDIO_3)具有很高的灵活性,可提供4种可编程的串口操作模式,1位串行2线模式、1位串行3线模式、2位串行模式、4位串行模式。表1为4种模式的引脚配置表。

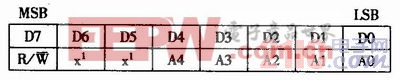

4个串行数据引脚中SDIO_1,SDIO_2,SDIO_3还可提供10位的输出振幅增减量。另外,SDIO_3还可用来提供SYNC_I/O功能,用以再同步串口控制器输出适当时序。AD9958的SCLK的最高频率是200 MHz,而4个串口数据引脚能进一步提高数据吞吐量,可达到800 Mbps。AD9958的串口操作是建立在寄存器级别上的,也就是说串口控制器能识别被访问的寄存器字节地址。在串行操作包括指令周期和通信周期,一般先传送指令周期,指令周期对应于SCLK的前8个上升沿,其对应的指令字(8比特)包含了以下信息:

D7位为R/W位,用于确定指令字后的操作是读还是写,高电平为读,低电平为写;D6、D5位为无关位;D4~D0位对应于A4~A0,表示随后的通信周期被访问的寄存器地址。

评论