一种基于稀疏矩阵的多核并行扰码方法

1.1 基于稀疏矩阵的多核并行扰码

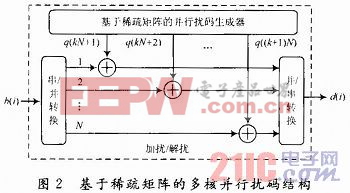

基于稀疏矩阵的多核并行扰码结构如图2所示。基于稀疏矩阵的并行扰码生成器产生了伪随机序列q,且同时输出序列q中N个相邻的伪随机码。此外,输入信号b(i)经过串/并转换后得到N路并行信号,然后分别送入对应序号的处理器核,在单个处理器核内,生成的伪随机码与输入信号进行模二加运算,得到输入信号的扰码输出;最后,并行扰码输出经过并/串转换得到串行扰码输出d(i)。本文引用地址:https://www.eepw.com.cn/article/155094.htm

图2中q(i)表示伪随机序列的第i个元素;k为非负整数;加法器表示模二加运算,则第i时刻扰码输出d(i)的数学表达式为:

d(i)=b(i)⊕q(i) (1)

从图2及式(1)可以看出,基于稀疏矩阵的并行扰码生成器是加扰,解扰过程中的重要组成部分。接下来详细介绍如何实现基于稀疏矩阵的并行扰码生成器。

假设并行扰码生成器输出的伪随机序列q为m序列,则q可由r级线性反馈移位寄存器产生,且其循环周期L=2r-1。r级线性反馈移位寄存器的生成多项式可写为:

式中c(n)取值为0或1。

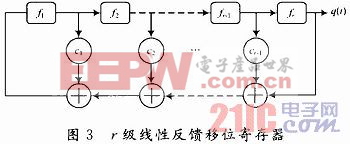

以式(2)作为生成多项式,图3给出了相应的r级线性反馈移位寄存器结构。

图中,q(i)表示第i时刻生成的伪随机码;fn代表寄存器;cn代表乘法器,加法器表示模二加运算,则i时刻的线性反馈移位寄存器状态为:

Fi=[f1i,f2i,…,fri]T (3)

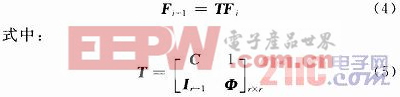

下一时刻,线性反馈移位寄存器的状态为:

评论