声纳信号处理中UDP协议数据传输研究与设计

摘要:为了在声纳系统中通过以太网口进行大批量、高速率的数据传输处理,在FPGA中硬件实现了嵌入式UDP协议栈,完成了架构设计、软件仿真验证及硬件实现。用FPGA硬件实现UDP协议栈,加速了网络数据处理能力,使信号传输速率达到了80MB/s,实现了千兆级通信,很好地提高了声纳系统中数据传输速率和系统性能。同时,用FPGA硬件实现UDP协议,栈减小了PCB版图面积和布局布线复杂度,提高了开发效率,有效地降低了开发成本。

关键词:UDP协议;FPGA;数据传输;信号处理

0 引言

UDP协议是一个简单的面向数据报的传输层协议,提供不呵靠的传输层服务。它只负责将应用数据打包交给网络层,但是不保证数据报能正确到达。UDP协议提供了一种最简单的基于数据包的、不可靠的传输机制。其特点是以数据包为最小传输单位,并且没有任何流量控制机制,适合传输效率要求较高且对传输可靠性要求不高的情况。

现有XXX型号声纳系统需要实现Link口转UDP格式数据传输,以满足大批量、高速率的数据传输要求,现有的CPU和软件协议栈无法满足此要求。经仔细研究,发现用FPGA硬件实现UDP协议栈,可以很好地提高数据传输速率,满足该声纳系统的性能要求。本文实现了一种可配置、可重用的硬件UDP协议栈,完成了UDP协议的FPGA设计:设计了UDP发送端模块,UDP接收端模块以及Link端模块等,同时对所设计系统进行了验证。经过实际验证,系统数据通信速率达到了80 MB/s,实现了千兆级以太网通信,很好地提高了声纳系统中数据传输速率和系统的性能,满足了XXX型声纳系统对大批量、高速率数据传输的要求。并且,此方案减小了PCB版图面积和布局布线复杂度,可以移植到任何其他的FPGA设计中,使开发效率得到了极大的提高,有效地降低了开发成本。

1 声纳系统信号处理中UDP协议的FPGA设计

1.1 UDP模块设计

UDP包头包括IP,端口号,UDP包长度,CHECKSUM四个部分。并且UDP信息包的标题很短(标题即头部),只有8 B,其中,源端口(2 B)、目的端口(2 B)、长度(2 B)、校验码(2 B)。这里设计的架构通过发送端对数据进行打包,通过接收端进行解包。

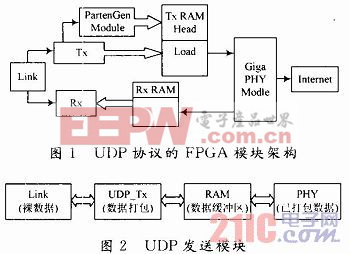

UDP协议的FPGA架构如图1所示。

发送端(Tx)是头信息生成模块,从Link口发出的数据传入发送模块Tx内。然后,发送模块Tx中的裸数据发送到数据缓冲区RAM中,经由PartenGen模块在数据前面添加首部,即为数据进行传输层协议UDP打包。传输层协议打包好的数据传输到物理层模块,通过物理层调节芯片传送到以太网口。发送完成后,发送模块恢复空闲状态,等待下一次数据发送。在发送过程中,传输数据的IP地址是固定的。UDP发送过程没

有可靠性的保证机制,只是进行数据的打包传输。发送模块结构图如图2所示。

评论