一种基于稀疏矩阵的多核并行扰码方法

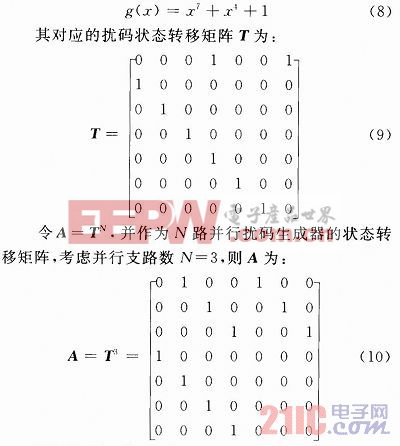

式中:r阶方阵T为r级线性反馈移位寄存器的状态转移矩阵;Ir-1表示r-1阶单位矩阵;C表示生成多项式的系数向量,如式(6)所示;φ表示r-1维全零列向量。

C=[c1,c2,…,cr-1] (6)

如图2所示,为了利用伪随机码q(i)对输入信号进行N路并行扰码,要求扰码生成器同时给出N路并行输出。在一个并行周期后,线性反馈移位寄存器的状态由Fi转换至Fi+N。

Fi+N=TNFi (7)

容易看出,式(7)所示的矩阵乘法运算完全等价于图3中线性反馈移位寄存器进行N次状态转换的结果,即该运算可实现一个N路并行扰码生成器,每个并行周期产生伪随机序列q的N路并行输出,同时将状态向量从Fi更新至Fi+N。考虑N≤r的情况,{f(r-N+1)i,f(r-N+2)i,…,fri}即为并行扰码生成器的输出向量。

如式(5)所示,由于状态转移矩阵T包含了r-1阶的单位矩阵以及r-1维全零列向量,不失一般性,且假设TN为稀疏矩阵。本文采用稀疏矩阵的存储及实现运算式(7)中的矩阵乘法,进而实现N路的并行扰码生成器,并将其定义为基于稀疏矩阵的并行扰码生成器。

1.2 稀疏矩阵的存储及运算

1.2.1 三元组存储

如式(8),以IEEE 802.11n使用的扰码生成多项式为例,说明如何利用稀疏矩阵的存储及运算实现并行的扰码生成器。

根据稀疏矩阵的三元组存储结构,将状态转移矩阵A存储为(i,j,aij)的形式,如图4所示。图中i表示行数,j表示列数,aij表示A中位于第i行第j列的元素。矩阵相乘时,矩阵A左乘列向量Fi,为方便对A进行遍历,在进行A的三元组存储时,先以行序号由小到大排列,同一行中再以列序号由小到大排列。

评论