使用Xilinx FPGA适应不断变化的广播视频潮流

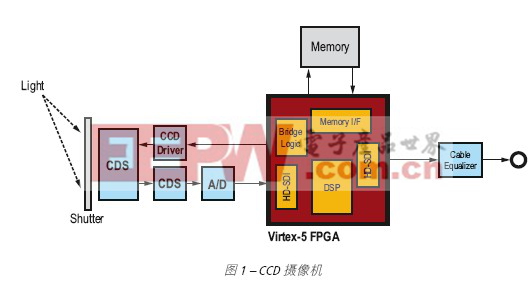

图1:电荷耦合器件(CCD)摄像机使用FPGA实现信号综合处理和颜色处理,并连接到CCD驱动器。CCD驱动器反过来驱使CCD、机械快门控制并触发控制。

一些视频制作中心开始使用以太网(Ethernet)通过网络传输水晶般剔透清晰的HD流。图像经过预处理和后处理,从而低延迟、实时地提高画面质量,然后使用各种编码和解码标准传输到网络中。由于流量很大且速率也非常快,所以数据必须经过压缩。例如,以30fps的速度传输1920x1080像素一次,在非压缩情况下所需数据速率达1.5Gbps。再添上多通道,所需速率就更高了。

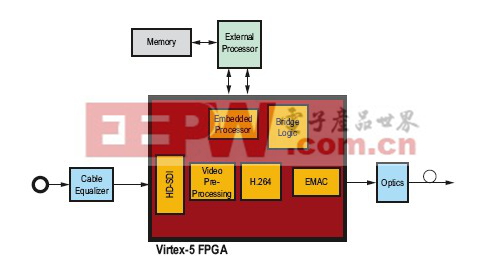

针对应用优化的FPGA具有嵌入式DSP模块、片上和片外存储器、丰富的逻辑应用,可构筑桥接功能,加上以太网和HD-SDI连接功能,对于创建上述系统来说,无疑是理想的解决方案。FPGA读取HD-SDI连接上显示的数据,然后对其进处理。编解码器(如H.264)可用于压缩数据。数据然后转换为以太网包,并包含在接收端进行解码所需的适当头(header)信息,最后使用MAC发送到以太网链路。

HDTV画面质量监视器

以前,消费者只能通过DVD访问高质量的视频和多通道音频内容。随着HD广播变得司空见惯,人们自然会将其与DVD相比。结果,电视观众对画面质量更加在意,尤其是HD。画面质量可能成为区分服务提供商高下的主要指标。现在人们急需的是能针对画面质量进行主观和客观测试,并可以测量可见误差的画面质量监视器。

图2所示为在Xilinx Virtex-5 FPGA中实现的一个画面质量监视器。客观测试使用了SMPTE RP 198中规定的常用的测试模式格式,而主观测试将广播馈送(broadcast feed)与本地测试视频源进行对比。FPGA从不同的源收集数据,进行预处理,然后将其发送到外部处理器进行分析。

该图为在Xilinx Virtex-5 FPGA中实现的一个画面质量监视器。FPGA从不同的源收集数据,进行预处理,然后将其发送到外部处理器进行分析。

实时HD AVC

高级视频编码(AVC)是一种视频压缩技术,此技术只需使用所需比特率的一半就可传输视频内容。AVC首次亮相是用于标准清晰度视频,但是对于HD服务商们,其吸引力更为巨大。AVC对运动补偿预测处理进行了大幅度的改进,从而使其领先MPEG-2一大截。AVC将运动预测精度增加了一倍,使用的模块尺寸更小(因其能更准确地跟踪对象),并且拥有更多的参考帧供搜索良好的运动预测匹配之用。这样,实时高清晰度AVC视频编码器只需MPEG-2一半的带宽就能以广播图像质量标准进行传输。

FPGA执行计算密集的运动估计任务的情况。运动估计通过使用计算绝对差而得出的重复总和而完成。数据对比是高度重复的,并且许多计算都重复使用。基于CPU的实现常常为从缓存向算术逻辑单元馈送数据而苦苦挣扎,而FPGA设计可以定制,从而在自定义寄存器流水线中保留所有值。

如Xilinx Virtex-5 FPGA这样的最新器件拥有大量的逻辑应用,能提供类似于ASIC级的性能。FPGA囊括了广播设备设计人员想要的所有功能:嵌入式低功耗3.2Gbps收发器;支持多种标准(如SDI、HD-SDI、双连接HD-SDI、3G-SDI、DVB-ASI、AES数字音频)、以太网和PCI Express接口、高速DSP模块、嵌入式处理器、以太网MAC、PCI Express核、多个视频IP核。

通过使用Xilinx芯片产品和广播设备进行视频连接应用设计,制造商可减少成本,在竞争中脱颖而出,同时降低更改标准所带来的固有风险。

评论