基于ISP技术的电子钟设计

要求能启动或停止电子钟运行,且能在电子钟停止运行状态下修改时、分、秒的值,可增加一个启动/停止控制端实现。如启动/停止控制端接低电平,分频模块的时钟接1 kHz的连续脉冲,其他模块分别接对应输出,电子钟便启动。而当启动/停止控制端接高电平,分频模块的时钟接地,其他模块的时钟分别接3个单脉冲手动输入,电子钟停止运行,手动产生一个单脉冲,与其相连的模块就计数一次,达到了修改时、分、秒的目的,即实现了电子钟更改时间的功能。本文引用地址:https://www.eepw.com.cn/article/148925.htm

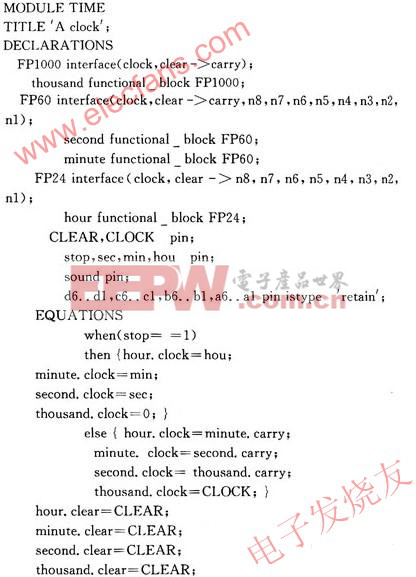

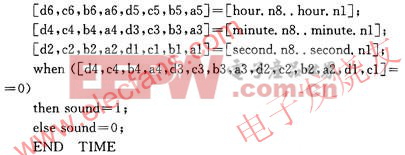

3.3 ABEL语言描述

下面用ABEL语言的层次结构实现电子钟的设计可分为顶层模块Clock,3个底层模块FP1000,FP60和FP24。下面介绍顶层模块CLOCK,其中调用了3个底层模块。

4 结 语

从上例可知,用ISP器件可进行各种数字电路实验,代替了古老的面模板实验,而且灵活方便,是一种较理想的数字电路课程设计方法,值得推广应用。

评论