分数阶Fourier变换应用于水声通信及其FPGA实现

复数结果的新表达式是:

本文引用地址:https://www.eepw.com.cn/article/146838.htm Rr=[(Ar+Ai)×(Br-Bi)]+(Ar×Bi-Ai×Br)(3次乘法) (8)

Ri=Ar×Bi+Ai×Br(复用来自Rr的乘积) (9)

综上可知:改进的复数乘法可用3个乘法器、3个加法器和2个减法器实现。在Cyclone系列FPGA中,每个8×8位乘法器需95个逻辑单元,而每个位宽16位的加法/减法模块只需18个逻辑单元,即改进后的复数乘法器减少41个逻辑单元,降低了FPGA的资源消耗。

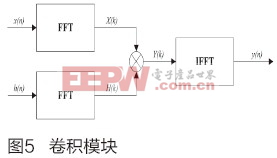

卷积模块

本文采用FFT运算完成卷积运算[11]。基于快速傅立叶变换的卷积计算流程如图5所示。分别对x(n)和h(n)进行FFT运算,得到对应的频域响应X(k)和H(k),将X(k)和H(k)相乘的结果再做IFFT,即可以得到x(n)和h(n)的卷积结果y(n)。

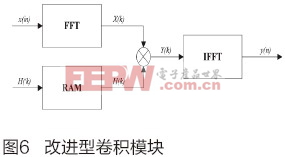

由于进行卷积的Chirp信号已知,为了降低FPGA的资源消耗,可预先计算Chirp信号的FFT结果,并将其保存到RAM中,即可减少一次FFT硬件运算。其改进快速傅立叶变换的卷积计算流程示意图如图6。

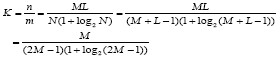

两次FFT运算共需要2×1/2Nlog2N次相乘还有N次相乘,因此共需要相乘次数为m=N(1+lbN)。传统方法直接计算线性卷积需要n=ML次乘法。当x(n)和h(n)点数相同时,则M=L,传统直接计算方法与改进方法进行卷积计算的运算量[12]比较为:

(10)

(10)

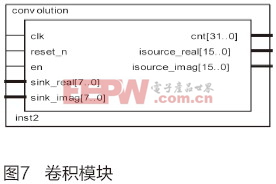

由式(10)可知M值越大,此算法的优越性越明显。用硬件语言设计出改进快速傅立叶变换的卷积部分并生成模块,如图7所示。

fpga相关文章:fpga是什么

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论