具有抗混叠滤波器和184.32 MSPS采样速率的高性能65 MHZ带宽四通道中频接收机

滤波器和接口设计程序

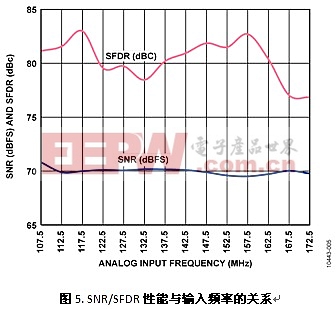

本文引用地址:https://www.eepw.com.cn/article/131809.htm本节介绍放大器/ADC与滤波器接口设计的常用方法。为了实现最佳性能(带宽、SNR、SFDR等),放大器和ADC应对一般电路形成某些设计限制:

放大器应参考数据手册推荐的正确直流负载,以获得最佳性能。

放大器与滤波器的负载间必须使用正确数量的串联电阻。这是为了防止通带内的不良信号尖峰。

ADC的输入应通过外部并联电阻降低,并使用正确串联电阻将ADC与滤波器隔离开。此串联电阻也会减少信号尖峰。

此设计方法倾向于利用大多数高速ADC的相对较高输入阻抗和驱动源的相对较低阻抗,将滤波器的插入损耗降至最低。

设计程序的详情请参见电路笔记 CN-0227 和 CN-0238。

评论