雷卯TVS和fuse助力DDR5 R-DIMM模组满足JEDEC新静电要求

DDR(Double Data Rate,双倍数据速率)是一种广泛应用于计算机和电子设备的高性能内存技术,DDR的主要应用于计算机系统,移动设备,嵌入式系临时存储和高速传输数据。因此,DDR是现代计算及移动系统的核心组件。

随着AI和大数据应用的爆发,DDR5 R-DIMM的高带宽(如5600 MT/s)和大容量(32GB)将成为关键优势,尤其在训练大型模型或处理实时数据时,可显著减少延迟。但JEDEC对DRAM 提出了一些新的要求。

一、JEDEC 对 DRAM PCB 静电的要求

JESD625C标准4:针对处理静电放电敏感(ESDS)设备的要求,该标准提供了一系列的防护措施和管理流程。对于 DRAM PCB 而言,相关要求包括:

l 静电放电控制措施:在生产、运输和使用过程中,要求采取防静电包装、使用防静电工作台、手腕带和防静电鞋等措施,以降低静电对 DRAM PCB 的潜在损害。

l 工作区设立:需要设立静电控制区域,明确 ESD 敏感区域和非敏感区域的界定、标识和管理。

l 设计建议:鼓励设计者在电路设计中加入 ESD 保护机制,如静电二极管,以增强电路板对静电放电的抵抗能力。

JESD22-C101F 标准以此来评估 DRAM PCB 等微电子元件在遭遇静电放电时的耐受能力。

JESD22-A114 标准规定了集成电路和组件针对人体模型(HBM)静电放电的测试方法和要求:JESD22-A115 标准规定了扩散模型(CDM)静电放电的测试方法和要求。这些标准从不同角度对DRAM PCB 可能面临的静电放电情况进行规范和测试指导。

随着技术发展,一些新的 DRAM PCB 设计采用了更先进的防护措施,如芝奇正在研发的由 16 层 PCB 打造的 DDR5 R-DIMM 模组,新增了瞬态电压抑制器TVS二极管及保险丝,以提升过电流保护并防止静电放电。这也反映了 JEDEC 标准在推动行业采用更可靠的防护技术方面的作用。

二、雷卯助行DDR5 R-DIMM 模组安全性

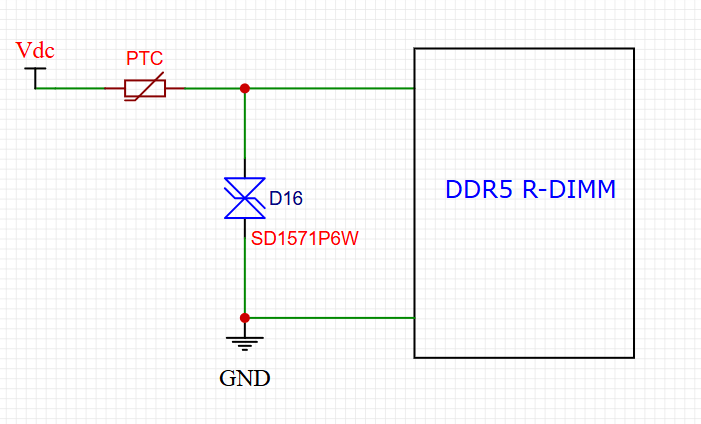

为防止瞬态电压与静电放电 (ESD),R-DIMM 模组直接从主板获取 12V 电压输入,因此需要先进的保护机制。雷卯为每个模组均配备高质量瞬态电压抑制 (TVS) 二极管与SMT保险丝。双重保护机制确保模组具备卓越的耐用性与长期稳定的性能。

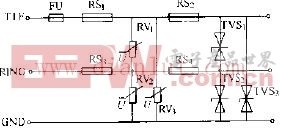

方案图如下:

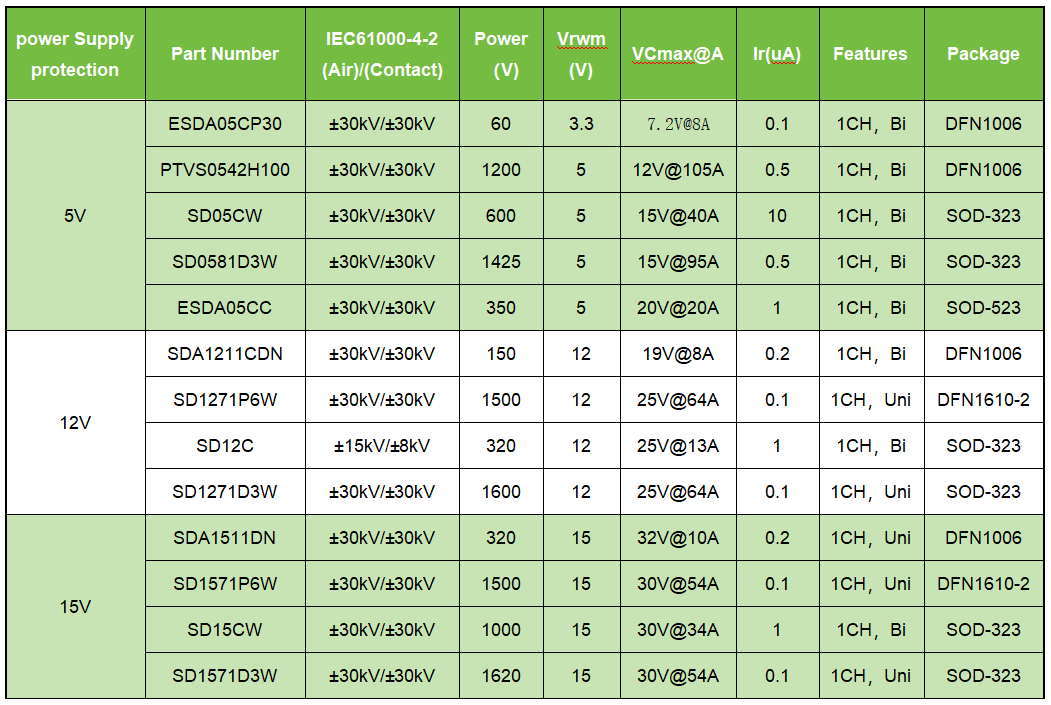

四. DDR5 R-DIMM的TVS二极管选择及推荐型号

TVS选择:选择ESD保护器件的反向截止电压(VRWM)略高于R-DIMM电源电压,脉冲耐受能力可以选大一点。

TVS放置:TVS靠近电源输入接口,确保ESD电流优先通过TVS泄放至地。TVS置于滤波电感前端,防止电感阻碍ESD电流泄放。使用短而宽的走线连接TVS与电源/地。地平面完整,避免分割,采用多点接地降低阻抗。

以下列出常规DDR5电源电压用TVS二极管,功率相对大,瞬态吸收电流大(IPP大),能有效抑制瞬态电压和ESD静电。

以上列出部分型号,如有其它电压需求请联系上海雷卯EMC小哥或销售人员获取支持。

对于选用的PPTC 上海雷卯提供多种封装、电流、电压需求, 封装有0603,0805,1206,1210,1812,2920,电流从0.05A 至7A 都有提供。可以根据需求选型。

Leiditech雷卯电子致力于成为电磁兼容解决方案和元器件供应领导品牌,供应ESD,TVS,TSS,GDT,MOV,MOSFET,Zener,电感等产品。雷卯拥有一支经验丰富的研发团队,能够根据客户需求提供个性化定制服务,为客户提供最优质的解决方案。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。